# Fondamenti di Elettronica Tutorato Dicembre 2024/Gennaio 2025

## Secondo incontro 10 Dicembre 2024 ore 16:30 Aula Alpha (edificio 24)

#### Dr. Maurizio Ghisetti

#### **Esercizio 1**

Si consideri il circuito mostrato in Fig. 1. Il generatore di corrente  $I_{in}$  genera un singolo impulso di corrente di ampiezza A pari a 2 mA e durata  $\Delta T$  pari a 10  $\mu s$ . Si assuma per il diodo D una tensione di accensione pari a 0.7 V.

a. Tracciare il diagramma temporale, quotandone tutti i punti significativi, della tensione di uscita  $V_{out}$

#### Esercizio 2

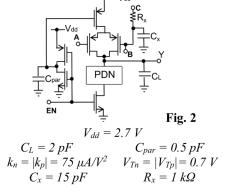

Si consideri il circuito logico riportato nella Fig. 1.

- a) Determinare la funzione logica svolta dal circuito logico e disegnare la rete di *pull-down* da sostituire alla resistenza *R* per realizzare la corrispondente porta in tecnologia *CMOS*.

- b) Determinare il tempo di transizione 20%-80% della tensione di uscita  $V_{out}$  nel circuito logico di Fig. 1 e nella corrispondente porta logica CMOS, a seguito della commutazione  $A = B = C = 0 \implies A = B = C = 1$ .

- c) Determinare il valore logico ed il corrispondente valore analogico di  $V_{out}$  per A = C = 1 e B = 0 e per A = B = C = 0.

### **Esercizio 3**

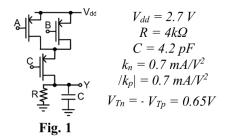

Si consideri il circuito logico, in tecnologia CMOS, riportato nella Fig. 2.

- a) Scrivere la tabella della verita' riportando il valore logico della tensione di uscita Y per ogni combinazione dei segnali di ingresso A e B e del segnale di controllo EN. Disegnare la rete di pull-down in tecnologia CMOS. Si trascuri la rete dall'ingresso C all'ingresso B.

- b) Determinare la potenza dissipata dalla porta nel caso di EN = 1 e di EN = 0, nel caso in cui gli ingressi A e B siano cortocircuitati tra loro e pilotati da un segnale logico a frequenza  $f_{ck} = 6$  MHz. L'ingresso C sia non connesso.

- c) Si consideri ora la rete dall'ingresso C all'ingresso B e si supponga di pilotare gli ingressi A e C cortocircuitati tra loro con un segnale logico a frequenza  $f_{ck} = 6$  MHz e di fissare EN = 1. Tracciare in 4 diagrammi temporali allineati, quotandone tutti i punti significativi, l'andamento delle forme d'onda in A, C, B e Y. Si assuma la soglia logica pari a  $V_{dd}/2$ .