# Fondamenti di Elettronica - AA 2002/2003 1<sup>a</sup> prova - Recupero 18 febbraio 2003

Indicare chiaramente la domanda a cui si sta rispondendo. Ad esempio 1a) ...

### **Esercizio 1**

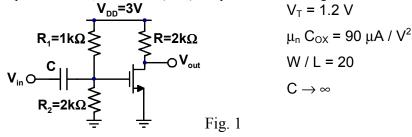

Dato il circuito in Fig. 1:

- a) Polarizzare e calcolare il guadagno di piccolo segnale *Vout/Vin*.

- b) E' possibile aumentare il modulo del guadagno fino a 5 variando R ? Giustificare la risposta e, in caso affermativo, calcolare R.

- c) E' possibile aumentare il modulo del guadagno fino a 7 variando R ? Giustificare la risposta e, in caso affermativo, calcolare R.

- d) Si assuma ora  $R=2k\Omega$ . Mostrare che è possibile raddoppiare il modulo del guadagno, mantenendo costante la corrente di polarizzazione, cambiando (W/L) e la polarizzazione del gate. Calcolare i nuovi valori di (W/L) e di tensione di gate.

## Esercizio 2

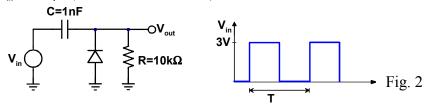

Dato il circuito in Fig.2

- a) In assenza del diodo, disegnare qualitativamente l'andamento temporale di  $V_{out}$  a regime quando il periodo del segnale in ingresso  $V_{in}$  e' T=100 $\mu$ s.

- b) **Sempre in assenza del diodo**, disegnare qualitativamente l'andamento temporale di  $V_{out}$  a regime quando il periodo del segnale in ingresso  $V_{in}$  e' T=1 $\mu$ s. (*Suggerimento*: qual è il valor medio di  $V_{out}$ ?)

- c) Si consideri adesso la presenza del diodo. Disegnare l'andamento temporale di  $V_{out}$  a regime quando il periodo del segnale in ingresso  $V_{in}$  e' T=1 $\mu$ s. (Si assuma il diodo ideale)

#### Esercizio 3

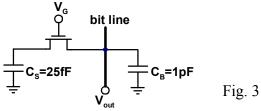

Si consideri la cella elementare di memoria dinamica in Fig.3, l'alimentazione è  $V_{dd}$ =3V,  $C_B$  è la capacità parassita della bit line

- a) Si ricorda che la bit-line prima della lettura viene pre-caricata a  $V_{dd'}/2$  (tensione iniziale su  $C_B=V_{dd'}/2$ ). Calcolare il valore finale dell'uscita (*espresso in Volt*) quando nella cella è memorizzato il valore 0 e quando è memorizzato il valore 1. Si consideri l'n-MOS un interruttore ideale

- b) Nel caso in cui nella cella e' memorizzato uno 0, cambia il valore finale dell'uscita se si considera l'nMOS con soglia  $V_T$ =0.5 V? Giustificare la risposta.

- c) Perché è necessario il refresh periodico delle memorie dinamiche come quella schematizzata? (Rispondere sinteticamente, utilizzare al massimo 5 righe di testo formule incluse)

## Esercizio 4

Un processore a CMOS, operante a 650 MHz richiede 10 W di potenza.

- a) Considerando il circuito composto esclusivamente di porte CMOS che dissipano solo potenza dinamica, che valore di dissipazione di potenza ci si attende quando la frequenza di clock è ridotta a 260 MHz?

- b) Poiche' il circuito, in realta', dissipa sia potenza dinamica che potenza statica (ossia quella dissipata da circuiti "di servizio" non commutanti, da correnti di perdita etc...), quando la frequenza viene effettivamente portata a 260 MHz, il valore di dissipazione scende a 5 W e non al valore precedentemente calcolato. Con i dati a disposizione determinare la potenza statica dissipata dal processore.