## Fondamenti di Elettronica

20 Nov. 2001

# Soluzioni "stringate"

#### **Es.** 1

Sia dato un transistore MOSFET a canale n.

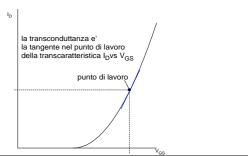

- a) Definire analiticamente la trasconduttanza quando il MOSFET funziona in saturazione ed esprimerla in funzione delle grandezze di

- b) Illustrare graficamente il significato della trasconduttanza.

a)  $g_m = 2k(V_{GS} - V_T) = 2\sqrt{kI_D}$

## **Es. 2**

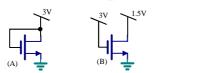

- a) Dire in che zona di funzionamento si trovano i MOSFET nei due casi in figura, spiegandone il perché.

- b) Calcolare la corrente di drain in almeno uno dei due casi.

$$V_T = 1V$$

$K = 1/2 \text{MINC}_{ox} \text{MV}/L = 0.3 \text{mA}/V^2$

MOSFET A: opera in zona di saturazione (c'e' canale al source e pinch-off in prossimita' del drain)

MOSFET B: opera in zona ohmica (c'e' canale sia al source che al

b)  $I_{DA} = k(V_{GS} - V_T)^2 = 1.2 \, mA$  $I_{DB} = k \left[ 2(V_{GS} - V_T)V_{DS} - V_{DS}^2 \right] = 1.125 \, mA$

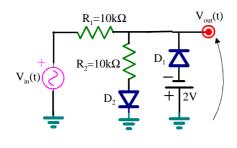

#### **Es. 3**

Il segnale è sinusoidale del tipo  $V_{in}(t)=5 \times in(\mathbf{w}t)$  [V]. Si modellizzino i diodi con una soglia di "accensione" di 0.7V.

- a) Indicare quale diodo si accende e per quale valore di  $V_{in}$  avviene l'accensione sia nel semiperiodo positivo che negativo.

- b) Disegnare l'andamento di  $V_{out}(t)$  in un periodo di  $V_{in}$ .

semiperiodo positivo: D1 off – D2 on per  $V_{in} \ge 0.7V$ , D2 off per  $V_{in} < 0.7V$ semiperiodo negativo: D2 off - D1 on per V<sub>in</sub>≤-2.7V, D1 off per V<sub>in</sub>>-2.7V

ut=0.7+(Vin-0.7)\*R2/(R1+R2) punto angoloso

## **Es. 4**

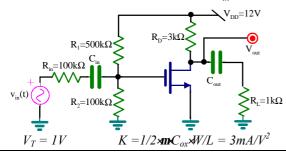

Nell'amplificatore in figura si ha  $C_{in} >> C_{out}$ . Calcolare:

- a) la polarizzazione (correnti e tensioni, senza segnale).

- b) il guadagno  $v_{out}/v_{in}$  a media frequenza ( $C_{in}$  in "corto",  $C_{out}$  "aperta");

- c) il guadagno  $v_{out}/v_{in}$  ad alta frequenza ( $C_{in}$  e  $C_{out}$  in "corto").

- d) Discutere infine la funzione del condensatore  $C_{in}$ .

- $V_G = 2V; V_D = 3V; V_{out} = 3V; V_{RL} = 0V;$  $I_{R1} = 20\mu A$ ;  $I_{R2} = 20\mu A$ ;  $I_{D} = 3mA$ ;  $I_{RL} = 0V$

- b)  $g_m = 6mA/V$ ;  $v_{out} / v_{in} = -g_m R_D \frac{R_1 \| R_2}{R_1 \| R_2 + R_{in}} = -8.2$ c)  $v_{out} / v_{in} = -g_m (R_D \| R_L) \frac{R_1 \| R_2}{R_1 \| R_2 + R_{in}} = -2.05$

- d) Il condensatore C<sub>in</sub> serve per disaccoppiare il generatore di segnale v<sub>in</sub> dal gate in modo da non alterare il punto di polarizzazione del transistore. C<sub>in</sub> e' un circuito aperto per la continua e deve essere dimensionata in maniera tale da essere un cortocircuito per tutte le frequenze di segnale di

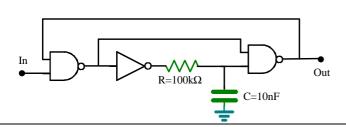

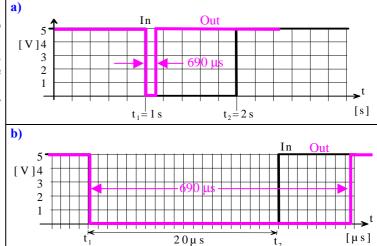

### **Es. 5**

Al circuito riportato in basso si applica l'ingresso mostrato qui a lato, caratterizzato dall'essere *low* per un tempo di *Is*.

- a) Disegnare l'andamento temporale dell'uscita Out, considerando nullo il ritardo di propagazione delle porte e pari a  $V_{DD}/2$  la loro soglia di commutazione.

- b) Dire cosa cambia se l'ingresso *In* resta basso per soli  $20\mu s$  (ossia  $t_2=t_1+20\mu s$ ).

#### **Es.** 6

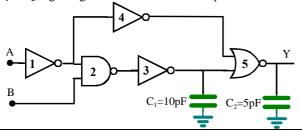

Il circuito è alimentato a 5V.

- a) Scrivere la tabella della verità della funzione implementata.

- b) Calcolare il ritardo di propagazione ingresso-uscita quando agli ingressi A e B connessi insieme si applica la transizione *high-low* (ignorare la presenza di  $C_1$  e  $C_2$  e supporre che il ritardo di propagazione di ciascuna porta sia  $t_P$ =50ns).

- c) Calcolare la potenza dinamica dissipata da ciascuna porta quando A=low e B è un clock a IMHz, sapendo che oltre a  $C_I$  e  $C_2$ , ogni ingresso contribuisce con 3pF.

| a) |          |   |   |

|----|----------|---|---|

|    | A        | В | Y |

|    | 0        | 0 | 1 |

|    | $0 \\ 0$ | 1 | 0 |

|    | 1        | 0 | 0 |

|    | 1        | 1 | 0 |

$T_{p \text{ max}} = t_{p1} + t_{p4} + t_{p5} = 150 \text{ns}$

$$P_1 = 0$$

$$P_2 = 75 \text{ mW}$$

$$P_3 = 325 \text{ mW}$$

$$P_5 = 125 \text{ mW}$$

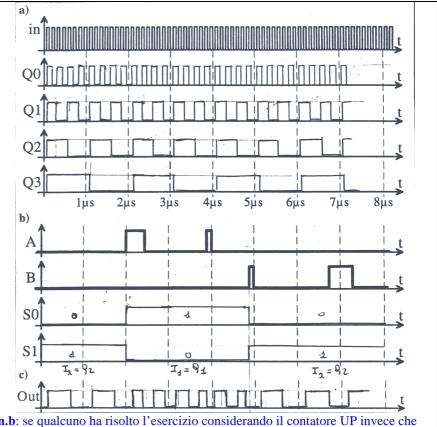

DOWN ma e' coerente con se stesso, va bene ugualmente.

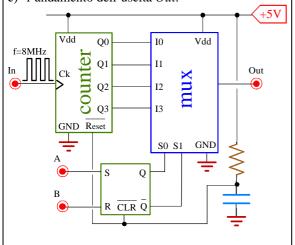

## **Es.** 7

All'instante t=0 il circuito viene alimentato a 5V; sempre a t=0 la rete RC assicura un istantaneo reset automatico del counter modulo-16 e del flipflop. I segnali di comando sono mostrati qui a lato; il clock è a 8MHz. Il flip-flop è di tipo attivo alto (ossia quando si asserisce S, Q va high).

Disegnare:

- a) gli andamenti delle uscite Q0÷Q3 del counter.

- b) gli andamenti degli ingressi S0 e S1 del mux.

- c) l'andamento dell'uscita Out.