# Politecnico di Milano

# Microcontrollori 2/3

ing. Enrico Migliore

Fondamenti di Elettronica

# Porte di I/O

| Tipologie:                                                                                                                     | MODE                                    | AVAILABLE ON(1)                        | SCHEMATIC         |

|--------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|----------------------------------------|-------------------|

| <ul> <li>Input digitale</li> <li>ingresso CMOS normale</li> <li>o a trigger di Schmidt</li> <li>a volte con pull-up</li> </ul> | Input                                   | PA0-PA7<br>PB0-PB5, PB6-PB7<br>PC0-PC4 | Data in Interrupt |

| - Input con Interrupt                                                                                                          | Input<br>with pull up                   | PA0-PA7<br>PB0-PB5, PB6-PB7<br>PC0-PC4 | Data in           |

| •abilitato a generare<br>•un interrupt nel μC                                                                                  | Input<br>with pull up<br>with interrupt | PA0-PA7<br>PB0-PB5, PB6-PB7<br>PC0-PC4 | Data in           |

| <ul> <li>Input analogico</li> <li>•per inviare segnali</li> <li>•analogici all'ADC del μC</li> </ul>                           | Analog Input                            | PA0-PA7<br>PC0-PC4                     | ADC               |

|                                                                                                                                | Open drain output<br>5mA                | PA0-PA7<br>PC0-PC4                     |                   |

| - Output digitale                                                                                                              | Open drain output<br>20mA               | P80-P85, P86-P87                       | Data out          |

| <ul><li>normalmente livelli CMOS</li><li>a volte open-drain</li><li>può avere pull-up interno</li></ul>                        | Push-pull output<br>5mA                 | PAO-PA7<br>PCO-PC4                     | Data out          |

| •può essere tri-state                                                                                                          | Push-pull output<br>20mA                | PB0-PB5, PB6-PB7                       |                   |

### Porte di I/O

# Inizializzazione interna dei pin di I/O:

#### PIC16C74A:

#### **INITIALIZING PORTA: EXAMPLE**

CLRF PORTA BSF STATUS, RPO

MOVLW 0xCF

MOVWF TRISA

; Initialize PORTA by clearing output latches ;Select Bank 1

;initialize data direction 11001111

;Set RA<3:0> as inputs ;RA<5:4> as outputs

;TRISA<7:6> always read as '0'

Note: I/O pin has protection diodes to VDD and Vss.

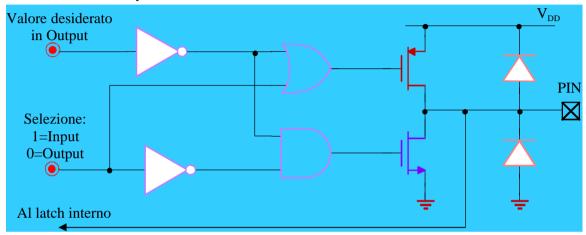

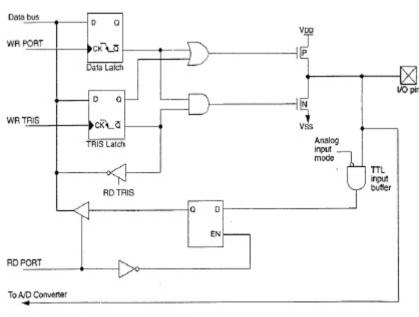

## Porte di I/O

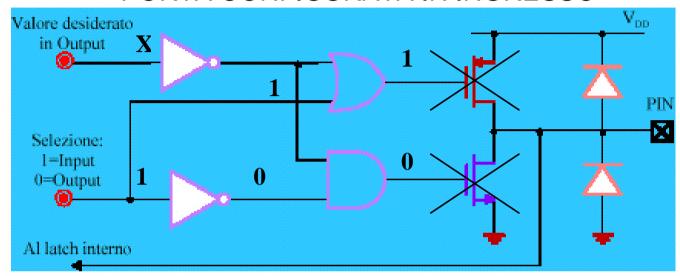

### PORTA CONFIGURATA IN INGRESSO

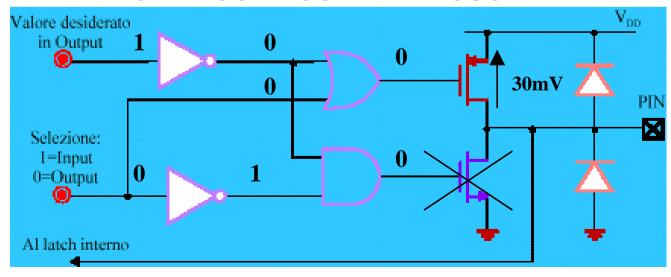

### PORTA CONFIGURATA IN USCITA

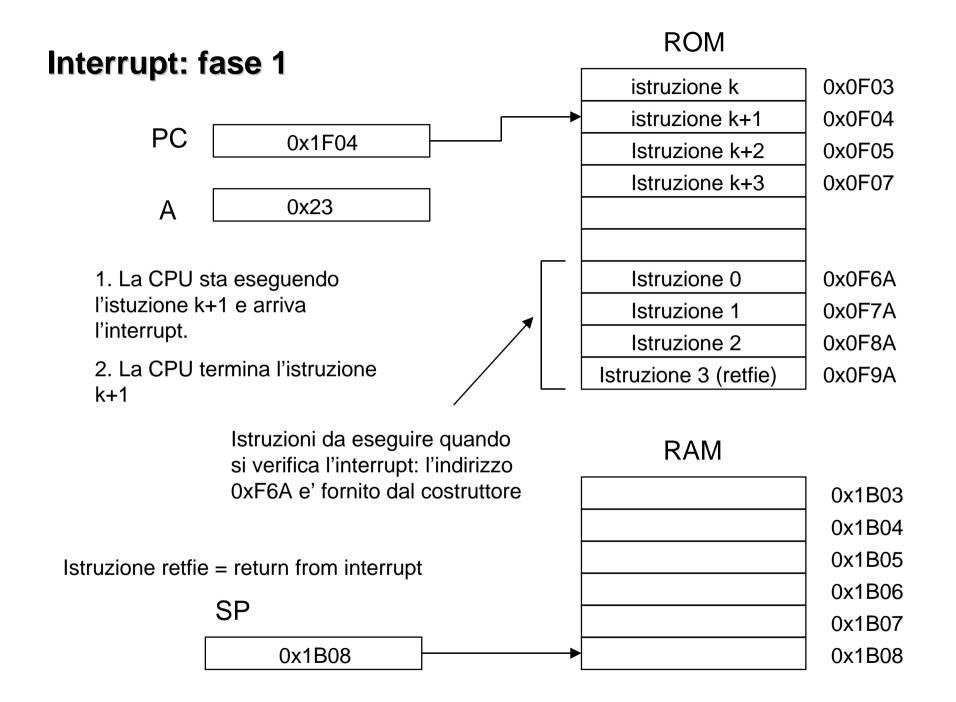

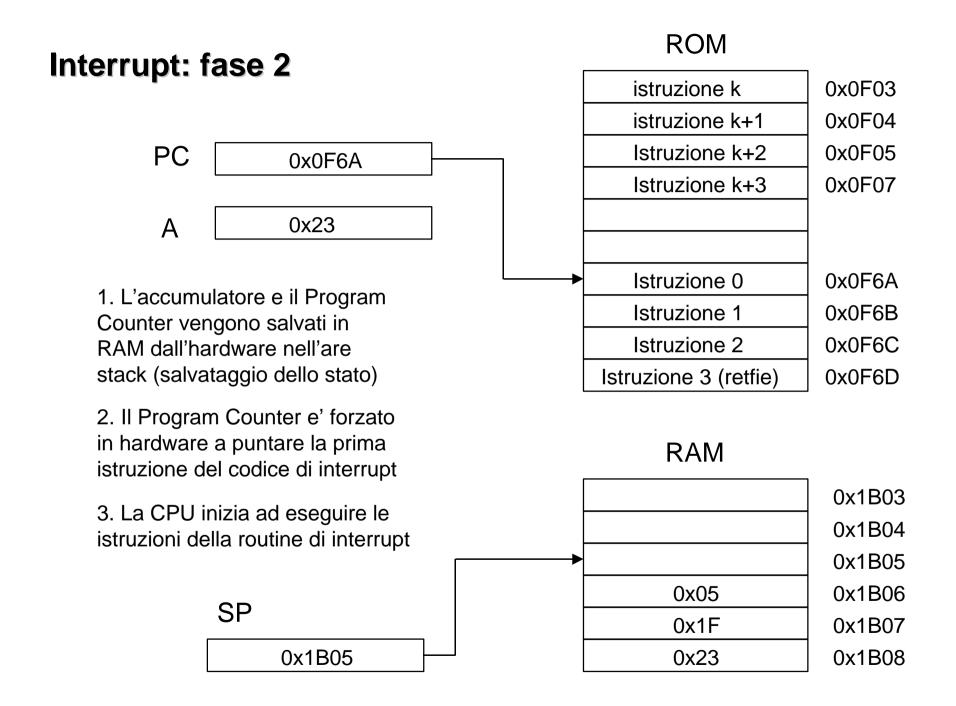

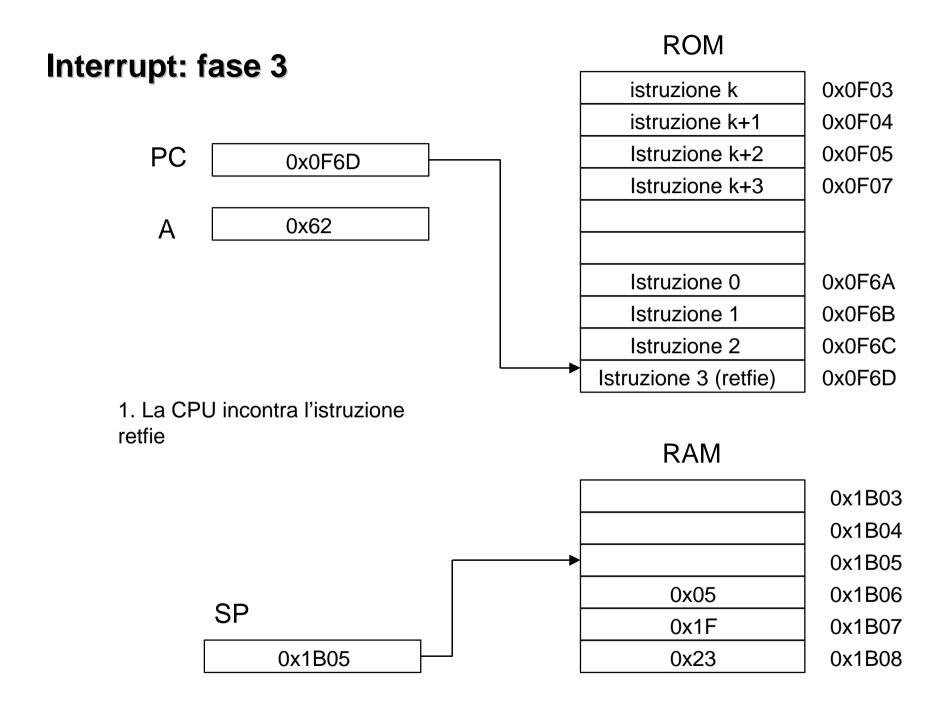

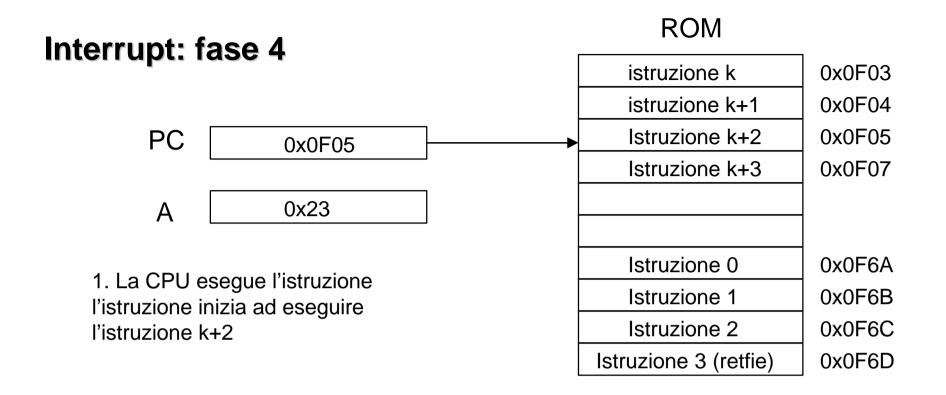

Idea base: la CPU sta eseguendo il programma principale. Si verifica un evento (es. un pin d'ingresso cambia stato) che necessita in tempi brevi di essere riconosciuto dalla CPU....

### Modalità di gestione:

- vettore di interrupt

- polling

ogni periferica chiamante ha la sua routine di gestione

c'è un'unica routine; il firmware dovrà individuare la periferica chiamante

### Stack:

- salvare il ProgramCounter

- salvare i registri importanti

per sapere da dove continuare, una volta gestita la routine di interrupt per evitare di modificare dati importanti

```

MOVWF

W_TEMP

;Copy W to TEMP register, could be bank one or zero

SWAPF

STATUS, W

;Swap status to be saved into W

ECF

STATUS, RPO

; Change to bank zero, regardless of current bank

MOVWF

STATUS_TEMP

; Save status to bank zero STATUS TEMP register

: (ISR)

SWAPF

STATUS_TEMP, W

;Swap STATUS_TEMP register into W

; (sets bank to original state)

MOVWE

STATUS

; Move W into STATUS register

SWAPF

W_TEMP, F

; Swap W TEMP

SWAPF

W_TEMP, W

;Swap W_TEMP into W

```

#### Utilità:

• gestire eventi imprevedibili allarme, finecorsa, pulsante...

• evitare cicli di attesa non si continua a monitorare l'evento, poiché sarà lui a chiamare

• eseguire prontamente routine per ogni chiamante si eseguiranno operazioni distinte

### Modalità di gestione:

• vettore di interrupt ogni periferica chiamante ha la sua routine di gestione

• polling c'è un'unica routine; il firmware dovrà individuare la periferica chiamante

### Stack:

• salvare il ProgramCounter

• salvare i registri importanti

per sapere da dove continuare, una volta gestita la routine di interrupt

MCVWF W\_TEMP ;Copy W to TEMP register, could be bank one or zero SWAPF STATUS,W ;Swap status to be saved into W BCF STATUS,RPO ;Change to bank zero, regardless of current bank MOVWF STATUS\_TEMP ;Save status to bank zero STATUS\_TEMP register : :(ISR)

per evitare di modificare dati importanti

:

SWAPF STATUS\_TEMP,W ;Swap STATUS\_TEMP register into W ; (sets bank to original state)

MOVWF STATUS ;Move W into STATUS register

SWAPF W\_TEMP,F ;Swap W\_TEMP

SWAPF W\_TEMP,W ;Swap W\_TEMP into W

### Gestione:

- impostando dei registri dedicati

- firmware della routine

abilitazione/disabilitazione dell'interrupt, flag dell'avvenuta chiamata...

#### INTCON REGISTER FOR PIC16C72/73/73A/74/74A (ADDRESS 0Bh, 8Bh)

|         | - 114      | TOOK                                       | LGISTE      | TONF        | 10100121                                    | 3// 3A//4                   | UA) API                    | DNESS UBII, OBII)                                                            |

|---------|------------|--------------------------------------------|-------------|-------------|---------------------------------------------|-----------------------------|----------------------------|------------------------------------------------------------------------------|

| R/W-0   | R/W-0      | Ft/W-0                                     | R/W-0       | R/W-0       | R/W-0                                       | R/W-0                       | R/W-x                      |                                                                              |

| GIE     | PEIE       | TOIE                                       | INTE        | RBIE        | TOIF                                        | INTF                        | RBIF                       | R = Readable bit                                                             |

| oit7    |            |                                            |             |             |                                             |                             | bitO                       | W = Writable bit U = Unimplemented bit, read as '0' - n = Value at POR reset |

| bit 7:  | GIE:(1) G  | lobal Inter                                | rupt Enab   | le bit      |                                             |                             |                            |                                                                              |

|         | 1 = Enab   | les all un-r<br>les all inte               | masked in   |             |                                             |                             |                            |                                                                              |

| bit 6:  | 1 = Enab   | ripheral In<br>les all un-<br>bles all per | masked p    | eripheral i | nterrupts                                   |                             |                            |                                                                              |

| bit 5:  | 1 = Enab   | R0 Overfloor<br>les the TM<br>ples the TM  | IR0 interr  | upt         | bit                                         |                             |                            |                                                                              |

| bit 4:  | 1 = Enab   | 30/INT Ext<br>les the RE<br>bles the RI    | 30/INT ext  | ernal inter | rrupt                                       |                             |                            |                                                                              |

| bit 3:  | 1 = Enab   | Port Cha<br>les the RE<br>ples the RI      | 3 port cha  | nge interr  | upt                                         |                             |                            |                                                                              |

| bit 2:  | 1 = TMR    | R0 Overfl<br>0 register<br>0 register      | has overf   | owed (mu    | t<br>ist be cleare                          | ed in softwa                | are)                       |                                                                              |

| bit 1:  | 1 = The f  | 80/INT Ext<br>RB0/INT e<br>RB0/INT e       | xternal in  | errupt occ  | bit<br>curred (mus<br>not occur             | t be cleare                 | d in softwa                | are)                                                                         |

| bit 0:  | 1 = At lea |                                            | the RB7:    | RB4 pins o  | bit<br>changed sta<br>hanged stat           |                             | e cleared in               | n software)                                                                  |

| Note 1: | may be ι   | unintention                                | nally re-en | abled by 1  | n interrupt of<br>the RETFIE<br>escription. | occurs while<br>instruction | le the GIE i<br>in the use | bit is being cleared, the GIE bit<br>'s Interrupt Service Routine.           |

#### PIE1 REGISTER PIC16C73/73A/74/74A (ADDRESS 8Ch)

| R/W-0    | R/W-0     | R/W-0                                    | R/W-0       | RW-0        | R/W-0        | R/W-0      | R/W-0  |                                                                              |

|----------|-----------|------------------------------------------|-------------|-------------|--------------|------------|--------|------------------------------------------------------------------------------|

| PSPIE(1) |           | RCIE                                     | TXIE        | SSPIE       | CCP1IE       | TMR2IE     | TMR1IE | R = Readable bit                                                             |

| bit7     |           |                                          |             |             |              |            | bit0   | W = Writable bit U = Unimplemented bit, read as '0' - n = Value at POR reset |

| bit 7:   | 1 = Enabl | Parallel S<br>les the PS<br>les the PS   | P read/wr   | ite interru |              | Enable bit |        |                                                                              |

| bit 6:   | 1 = Enab  | O Converte<br>les the A/E<br>les the A/I | interrupt   |             | oit          |            |        |                                                                              |

| bit 5:   | 1 = Enab  | SART Reco<br>les the US<br>bles the US   | ART rece    | ive interru | pt           |            |        |                                                                              |

| bit 4:   | 1 = Enab  | ART Tran<br>les the US<br>les the US     | ART trans   | smit intern | upt          |            |        |                                                                              |

| bit 3:   | 1 = Enab  | ynchrono<br>les the SS<br>les the SS     | P interrup  | t           | upt Enable i | bit        |        |                                                                              |

| bit 2:   | 1 = Enab  | CCP1 Intelles the CC                     | P1 interru  | upt         |              |            |        |                                                                              |

| bit 1:   | 1 = Enab  | TMR2 to<br>les the TM<br>bles the TM     | 1R2 to PR   | 2 match in  |              |            |        |                                                                              |

| bit 0:   | TMR11E:   | TMR1 Ov                                  | erflow inte | errupt Ena  | able bit     |            |        |                                                                              |

1 = Enables the TMR1 overflow interrupt 0 = Disables the TMR1 overflow interrupt

Note 1: PIC16C73 and PIC16C73A devices do not have a Parallel Slave Port implemented, this bit location is reserved on these two devices, always maintain this bit clear.

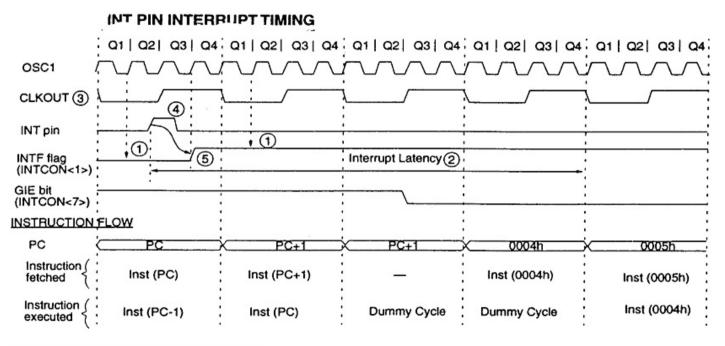

### Latenza:

- esecuzione non immediata della routine di interrupt

- temporizzazione

Note 1: INTF flag is sampled here (every Q1).

2: Interrupt latency = 3-4 Tcy where Tcy = instruction cycle time.

Latency is the same whether Inst (PC) is a single cycle or a 2-cycle instruction.

3: CLKOUT is available only in RC oscillator mode.

4: For minimum width of INT pulse, refer to AC specs.

5: INTF is enabled to be set anytime during the Q4-Q1 cycles.

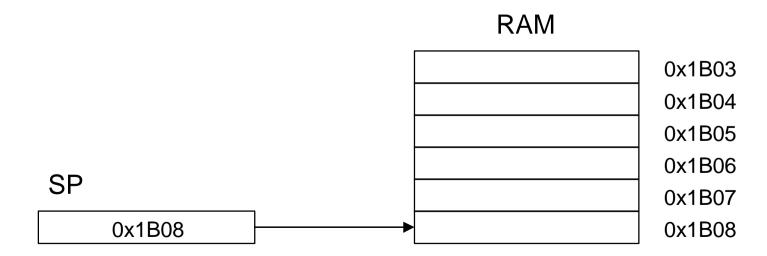

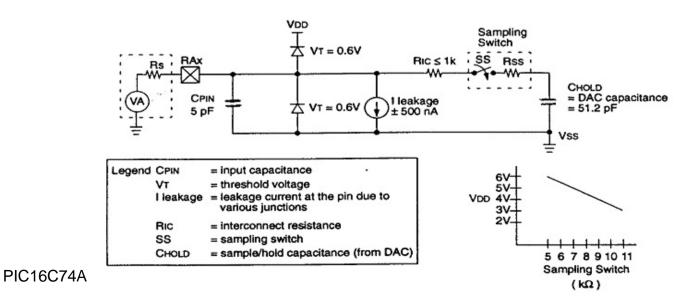

# Convertitore Analogico/Digitale:

- multiplexer analogico a più ingressi

- campionatore S&H

- ADC (SuccessiveApproximationRegister)

### Risoluzione:

• numero di bit

• FullScaleRange  $FSR = V_{ref}$

• LeastSignificantBit LSB =  $FSR / 2^n$

### Errori:

• statici correnti di leakage, resitenze parassite

$R_S < \frac{1}{2}LSB / I_{leakage} = 10k\Omega$

• dinamici carica esponenziale del condensatore del S&H

$$V_{ref} - \frac{1}{2}LSB = (1 - e^{-t/\tau}) \cdot V_{ref}$$

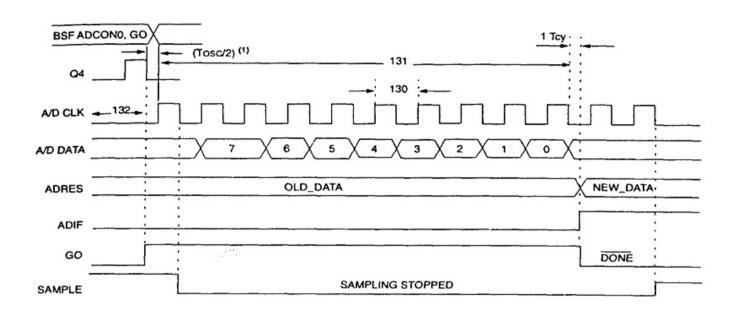

### Tempistiche:

• di acquisizione carica esponenziale di C<sub>HOLD</sub>

$$T_a = -C_{HOLD} (R_S + R_{IC} + R_{SS}) \cdot ln \frac{\frac{1}{2}LSB}{V_{ref}} = 5.7 \mu s$$

• di conversione durata della conversione nell'ADC

$$T_{conv} = 9.5 \cdot T_{AD}$$

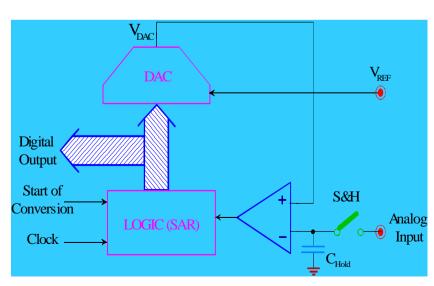

### Configurazione:

• tramite registri dedicati

#### ADCONO REGISTER, PIC16C72/73/73A/74/74A (ADDRESS 1Fh)

| R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 | R/W-0   | U-0               | R/W-0 |                          |

|-------|-------|--------|-------|-------|---------|-------------------|-------|--------------------------|

| ADCS1 | ADCS0 | CHS2   | CHS1  | CHS0  | GO/DONE | 5 <del>(=</del> 1 | ADON  | R = Readable bit         |

| bit7  |       | 200000 |       |       |         |                   | bit0  | W = Writable bit         |

|       |       |        |       |       |         |                   |       | U = Unimplemented bit,   |

|       |       |        |       |       |         |                   |       | read as '0'              |

|       |       |        |       |       |         |                   |       | - n = Value at POR reset |

bit 7-6: ADCS1:ADCS0: A/D Conversion Clock Select bits

00 = Fosc/2

01 = Fosc/8

10 = Fosc/32

11 = FRC (clock derived from an RC oscillation)

bit 5-3: CHS2:CHS0: Analog Channel Select bits

000 = channel 0, (RA0/AN0)

001 = channel 1, (RA1/AN1)

010 = channel 2, (RA2/AN2)

011 = channel 3, (RA3/AN3)

100 = channel 4, (RA5/AN4)

101 = channel 5, (RE0/AN5)(1)

110 = channel 6, (RE1/AN6)(1)

111 = channel 7, (RE2/AN7)(1)

bit 2: GO/DONE: A/D Conversion Status bit

If ADON = 1

1 = A/D conversion in progress (setting this bit starts the A/D conversion)

0 = A/D conversion not in progress (This bit is automatically cleared by hardware when the A/D conversion is complete)

bit 1: Unimplemented: Read as '0'

bit 0: ADON: A/D On bit

1 = A/D converter module is operating

0 = A/D converter module is shutoff and consumes no operating current

BSF STATUS, RPO ; Select Page 1

CLRF ADCON1 ; Configure A/D inputs BSF PIE1,ADIE ; Enable A/D interrupts

BCF STATUS, RPO ; Select Page 0

MOVLW 0XC1 ; A/D is on , Ch0 is selected

MOVWF ADCON0 ;

BCF PIR1, ADIF ; Clear A/D interrupt flag bit

BSF INTCON, PEIE ; Enable peripheral interrupts

BSF INTCON, GIE ; Enable all interrupts

:

BSF ADCON, GO ; Start A/D Conversion

:

#### ADCON1 REGISTER, PIC16C72/73/73A/74/74A (ADDRESS 9Fh)

| U-0    | U-0    | U-0                | U-0                  | U-0           | R/W-0 | R/W-0 | R/W-0 | 2 <u>-1-1-1-1</u>                  |

|--------|--------|--------------------|----------------------|---------------|-------|-------|-------|------------------------------------|

| The Co | 2 -12/ | # <del>- 1</del> 4 | - " <del>- "</del> % | % <b>–</b> `- | PCFG2 | PCFG1 | PCFG0 | R = Readable bit                   |

| bit7   |        |                    |                      |               |       |       | bit0  | W = Writable bit U = Unimplemented |

|        |        |                    |                      |               |       |       |       | bit, read as '0'                   |

|        |        |                    |                      |               |       |       |       | - n = Value at POR reset           |

bit 7-3: Unimplemented: Read as '0'

bit 2-0: PCFG2:PCFG0: A/D Port Configuration Control bits

| PCFG2:PCFG0 | RA0 | RA1 | RA2 | RA5 | RA3  | RE0 <sup>(1)</sup> | RE1 <sup>(1)</sup> | RE2 <sup>(1)</sup> | VREF |

|-------------|-----|-----|-----|-----|------|--------------------|--------------------|--------------------|------|

| 000         | Α   | Α   | Α   | Α   | Α    | Α                  | Α                  | A                  | VDD  |

| 001         | Α   | Α   | Α   | Α   | VREF | Α                  | Α                  | Α                  | RA3  |

| 010         | Α   | Α   | Α   | Α   | Α    | D                  | D                  | D                  | VDD  |

| 011         | Α   | A   | Α   | Α   | VREF | D                  | D                  | D                  | RA3  |

| 100         | Α   | Α   | D   | D   | Α    | D                  | D                  | D                  | VDD  |

| 101         | Α   | Α   | D   | D   | VAEF | D                  | D                  | D                  | RA3  |

| 11x         | D   | D   | D   | D   | D    | D                  | D                  | D                  | -    |

A = Analog input

D = Digital I/O

## Timing:

#### A/D CONVERSION REQUIREMENTS

| Parameter<br>No. | Sym  | Characteristic                                    |              | Min    | Тур†   | Max | Units | Conditions                  |  |

|------------------|------|---------------------------------------------------|--------------|--------|--------|-----|-------|-----------------------------|--|

| 130              | TAD  | A/D clock period                                  | PIC16C73/74  | 1.6    | _      |     | μs    | Tosc based, VREF ≥ 3.0V     |  |

|                  |      |                                                   | PIC16LC73/74 | 2.0    | _      | _   | μs    | Tosc based, VREF full range |  |

|                  |      |                                                   | PIC16C73/74  | 2.0    | 4.0    | 6.0 | μs    | A/D RC Mode                 |  |

|                  |      |                                                   | PIC16LC73/74 | 3.0    | 6.0    | 9.0 | μs    | A/D RC Mode                 |  |

| 131              | TCNV | Conversion time (not including S/H time) (Note 1) |              | -      | 9.5TAD | _   | _     |                             |  |

| 132              | TACQ | Acquisition time                                  |              | Note 2 | 20     | _   | μs    |                             |  |

- \* These parameters are characterized but not tested.

- † Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

- Note 1: ADRES register may be read on the following TcY cycle.

- 2: See Section 13.1 for min conditions.

### Specifiche elettriche:

| Parameter<br>No. | Sym  | Characteristic                                       | Min       | Typt       | Max                 | Units    | Conditions                                           |

|------------------|------|------------------------------------------------------|-----------|------------|---------------------|----------|------------------------------------------------------|

|                  | NR   | Resolution                                           | _         | _          | 8-bits              | _        | VREF = VDD = 5.12V, VSS ≤ AIN ≤ VREF                 |

|                  | NINT | Integral error                                       | _         | -          | less than<br>±1 LSb | -        | VREF = VDD = 5.12V, VSS ≤ AIN ≤ VREF                 |

|                  | NDIF | Differential error                                   | _         | _          | less than<br>±1 LSb | -        | VREF = VDD = 5.12V, VSS ≤ AIN ≤ VREF                 |

|                  | NFS  | Full scale error                                     | _         | _          | less than<br>±1 LSb | _        | VREF = VDD = 5.12V, VSS ≤ AIN ≤ VREF                 |

|                  | Noff | Offset error                                         | _         | _          | less than<br>±1 LSb | _        | VREF = VDD = 5.12V, VSS ≤ AIN ≤ VREF                 |

|                  | _    | Monotonicity                                         | _         | guaranteed | _                   | -        | Vss ≤ Ain ≤ VREF                                     |

|                  | VREF | Reference voltage                                    | 3.0V      |            | VDD + 0.3           | ٧        |                                                      |

|                  | VAIN | Analog input voltage                                 | Vss - 0.3 | _          | VREF + 0.3          | ٧        |                                                      |

|                  | ZAIN | Recommended<br>impedance of analog<br>voltage source | _         | _          | 10.0                | kΩ       |                                                      |

|                  | ÍAD  | A/D conversion cur-<br>rent (VDD)                    | _         | 180        | _                   | μА       | Average current consumption when A/D is on. (Note 1) |

|                  | IREF | VREF input current (Note 2)                          | _         | _          | 1<br>10             | mΑ<br>μΑ | During sampling All other times                      |

<sup>\*</sup> These parameters are characterized but not tested.

Note 1: When A/D is off, it will not consume any current other than minor leakage current. The power-down current spec includes any such leakage from the A/D module.

2: VREF current is from RA3 pin or VDD pin, whichever is selected as reference input.

Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

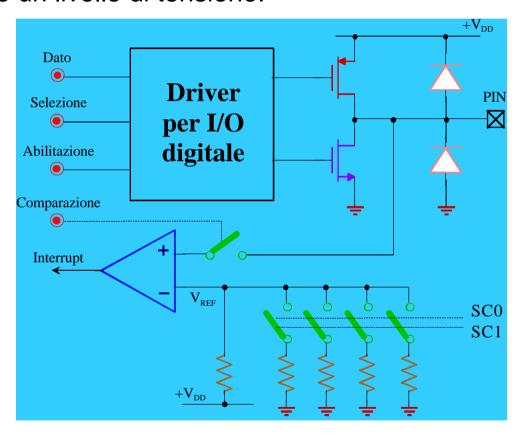

# **Comparatore o Watchdog analogico**

Per monitorare un livello di tensione:

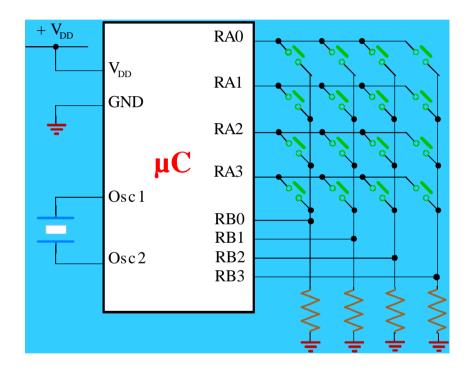

# Esempi di impiego degli I/O

Esempio 1: Multiplexing Digitale di una tastiera

Si risparmiano linee digitali

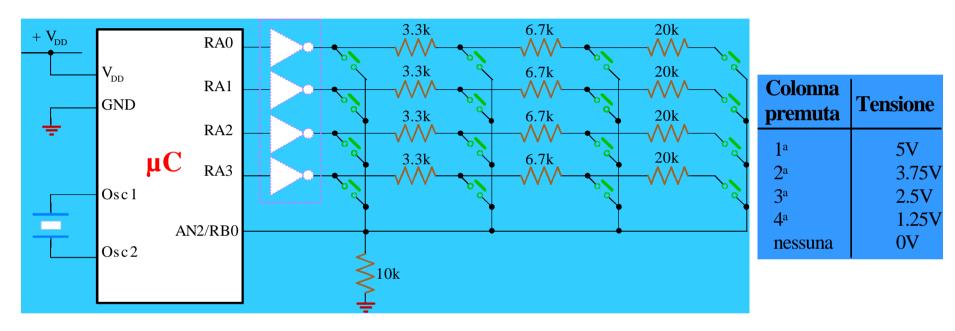

# Esempi di impiego degli I/O

Esempio 2: Acquisizione analogica

Si utilizza un ritorno analogico Gli si può fare scatenare un interrupt, ma...

$$V_{\text{max,min}} = 5 \cdot \frac{(10K \pm 10\%)}{(10K \pm 10\%) + (3.3K + 6.7K + 20K \text{ m}10\%)} V_{\text{max,min}} = 5 \cdot \frac{(10K \pm 10\%)}{(10K \pm 10\%) + (3.3K + 6.7K \text{ m}10\%)}$$