## **ESERCIZIO**

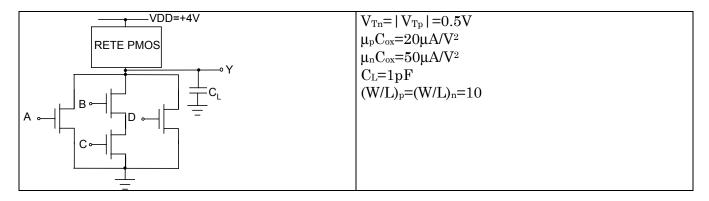

Si consideri la porta logica CMOS in figura

- a) Determinare la funzione logica realizzata dalla porta.

- b) Disegnare la rete di pull-down a NMOS, assegnata la rete dei PMOS.

- c) Si assuma che inizialmente A=B=C=0 e  $D=V_{DD}$ . All'istante t=0 D commuta da  $V_{DD}$  a 0. Disegnare qualitativamente l'evoluzione temporale di  $V_{out}(t)$  e calcolare approssimativamente il tempo di propagazione della commutazione.

- d) Calcolare il valore (W/L) dei transistori PMOS necessario perche' i tempi di propagazione t<sub>pLH</sub> e t<sub>pHL</sub> della porta logica siano uguali per le configurazioni di ingressi piu' gravose nei riguardi delle variazioni dell'uscita, assumendo (W/L)<sub>n</sub>=10.

## **SOLUZIONE**

a) La funzione logica realizzata dalla porta CMOS e':

$$Y = \overline{A + B \cdot C + D} = \overline{A} \cdot \overline{(B \cdot C)} \cdot \overline{D} = \overline{A} \cdot (\overline{B} + \overline{C}) \cdot \overline{D}$$

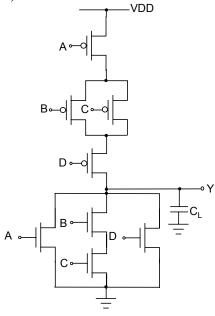

b) La rete dei PMOS e'il duale della rete degli NMOS

- c) Per la configurazione di ingressi A=B=C=0, D che commuta dal livello logico alto al livello logico basso:

- gli NMOS pilotati da A, B, C sono OFF

- i PMOS pilotati da A, B, C sono ON

- la commutazione di D da 1 a 0 fa spegnere il relativo NMOS ed accendere il relativo PMOS, quindi l'uscita commuta dal livello logico basso a quello alto.

La carica della capacita' C<sub>L</sub> avviene attraverso la rete di pull-up. Per calcolare il tempo di commutazione calcoliamo il (W/L) del PMOS dell'inverter equivalente.

I PMOS pilotati da B e da C sono tra loro in parallelo, per cui dobbiamo sommare i loro (W/L) per ottenere il (W/L) equivalente:

$$\left(\frac{W}{L}\right)_{p,eq(B,C)} = \left(\frac{W}{L}\right)_{p,B} + \left(\frac{W}{L}\right)_{p,C} = 2\left(\frac{W}{L}\right)_{p}$$

Avremo, quindi, la serie di tre PMOS, pilotati rispettivamente da A, (B+C), D che da' origine ad un PMOS dell'invertitore equivalente caratterizzato da

$$\left(\frac{L}{W}\right)_{p,eq} = \left(\frac{L}{W}\right)_{p,A} + \left(\frac{L}{W}\right)_{p,D} + \frac{1}{2}\left(\frac{L}{W}\right)_{p} = \frac{5}{2}\frac{L}{W}$$

La carica della capacita' avviene, quindi, mediante un PMOS equivalente con  $(W/L)=2/5(W/L)_p=4$ .

- Possiamo usare due diverse approssimazioni per calcolare il tempo di propagazione:

- 1. PMOS in zona ohmica

- 2. PMOS in zona satura

- 1. PMOS in zona ohmica: il circuito puo'essere schematizzato come segue

$$R_{DSon}$$

$C_L$

dove

$$R_{DSon} = \frac{1}{\frac{\partial I_{D}}{\partial V_{DS}}}\bigg|_{V_{DS}=0} = \frac{1}{2k_{p}(V_{GS} - V_{T})} = \frac{1}{2\frac{1}{2}\mu_{p}C_{ox}(\frac{W}{L})_{p,eq}(V_{GS} - V_{T})} = 3.6k\Omega.$$

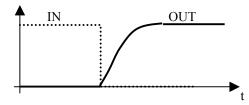

Il tempo di propagazione e' dato, in questo caso, da  $t_{p,LH} = \ln(2) \cdot \tau = 0.69 \cdot R_{DSon} \cdot C_L = 2.48 \, ns$

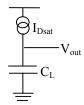

2. PMOS in zona satura: il circuito puo'essere schematizzato come segue

dove

$$I_{Dsat} = k_p (V_{GS} - V_T)^2 = \frac{1}{2} \mu_p C_{ox} \left(\frac{W}{L}\right)_{p,eq} (V_{DD} - V_T)^2 = 490 \mu A.$$

Il tempo di propagazione e' dato, in questo caso, da

$$t_{p,LH} = \frac{Q_{acc}}{I_{Dsat}} = \frac{C_L \frac{V_{DD}}{2}}{I_{Dsat}} = 4ns$$

d) Ricorriamo all'inverter equivalente caratterizzato da  $k_p$ = $k_n$ , quindi avente  $(W/L)_p$ =2.5 $(W/L)_n$ . Per  $t_p$ LH la situazione più gravosa si ha quando l'eventuale capacita' di carico e' caricata attraverso la serie dei PMOS A,B(C),D:

$$\left(\frac{W}{L}\right)_{p,eq} = \frac{1}{\left(\frac{L}{W}\right)_{p} + \left(\frac{L}{W}\right)_{p} + \left(\frac{L}{W}\right)_{p}} = \frac{1}{3}\left(\frac{W}{L}\right)_{p}$$

Per gli NMOS la situazione piu' gravosa si ha quando la scarica della capacita' avviene attraverso la serie dei due NMOS B,C:

det aue NMOS B,C:

$$\left(\frac{W}{L}\right)_{n,eq} = \frac{1}{\left(\frac{L}{W}\right)_n + \left(\frac{L}{W}\right)_n} = \frac{1}{2}\left(\frac{W}{L}\right)_n$$

Assumendo come riferimento l'inverter equivalente caratterizzato da  $(W/L)_n=10$  e  $(W/L)_p=2.5(W/L)_n$ , si ha:

$$\frac{1}{3} \left(\frac{W}{L}\right)_p = 2.5 \frac{1}{2} \left(\frac{W}{L}\right)_n$$

$$\left(\frac{W}{L}\right)_p = \frac{7.5}{2} \left(\frac{W}{L}\right)_n = 37.5$$

Questa scelta garantisce l'uguaglianza dei tempi di propagazione per la situazione piu' gravosa, mentre le combinazioni di ingressi che portano piu' di un MOSFET tra quelli in parallelo a condurre presenteranno tempi di propagazione minori.