## Fondamenti di Elettronica - Ingegneria Elettronica - a.a. 2014/15 2ª prova in itinere - 30 giugno 2015

Indicare chiaramente la domanda a cui si sta rispondendo. Ad esempio 1a) .... Risolvere per primi i punti in grassetto. La durata della prova e' 3 ore. Non sono ammessi libri o appunti o altro materiale, eccetto la calcolatrice.

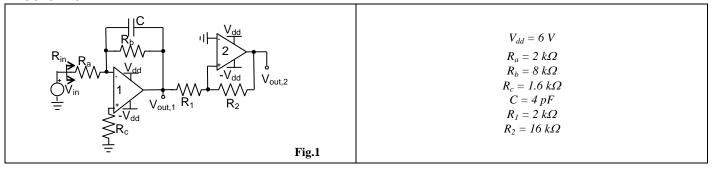

## Esercizio 1

Si consideri il circuito mostrato in Fig. 1. Si assuma che gli amplificatori operazionali saturino alle tensioni di alimentazione.

- a. Determinare l'espressione del trasferimento ideale  $V_{out,1}/V_{in}$ , specificando i valori del guadagno in continua e delle singolarita'.

- b.Determinare i valori della tensione  $V_{oub\,I}$  in grado di provocare una commutazione dell'uscita  $V_{oub\,2}$  mostrando in dettaglio i calcoli effettuati per determinare tali valori. Determinare, inoltre, il massimo valore r.m.s. del rumore sovrapposto al segnale di ingresso  $V_{in}$  che non causi commutazioni spurie. Si assumano gli amplificatori operazionali ideali e C un circuito aperto.

- c. Se entrambi gli amplificatori operazionali sono caratterizzati da un valor medio della corrente di bias  $I_{bias} = 150nA$  (entrante nei morsetti dell'operazionale), determinare l'effetto sulla tensione  $V_{out,1}$  e sulle soglie di scatto del circuito contenente il secondo operazionale.

- d. Calcolare l'espressione ed il valore della resistenza  $R_{in}$  se l'amplificatore operazionale 1 e' caratterizzato da un guadagno ad anello aperto  $A_0 = 100 \ dB$  e da una resistenza di ingresso differenziale  $R_{id} = 40 M \Omega$ .

- e. Determinare il margine di fase del circuito contenente l'amplificatore operazionale 1, se l'amplificatore operazionale 1 e' caratterizzato da un prodotto guadagno larghezza di banda GBWP = 90 MHz.

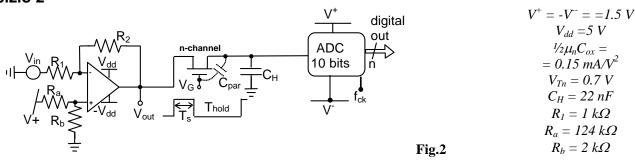

## Esercizio 2

Si consideri la catena di acquisizione mostrata nella Fig. 2. Si assuma che l'amplificatore operazionale saturi alle tensioni di alimentazione e che la tensione di ingresso abbia ampiezze comprese nell'intervallo (-50 mV, +100 mV).

- a) Determinare il valore della resistenza  $R_2$  necessario per sfruttare al pieno la dinamica dell'ADC, mostrando esplicitamente i calcoli effettuati per determinare tale valore. Determinare quindi la risoluzione in ingresso ottenibile.

- b) Assumendo che l'ADC sia caratterizzato da una resistenza di ingresso pari a 100 M $\Omega$ , determinare la massima durata del tempo di Hold nelle ipotesi di ammettere un errore massimo pari a 0.2 LSB.

- c) Assumendo che il transistore del circuito di Sample & Hold sia caratterizzato da una capacita' parassita ( $C_{par}$  mostrata in Fig. 2) pari a 900 fF e di lavorare con segnali che coprano l'intera dinamica dell'ADC, se la tensione  $V_G$  in fase di sample e' pari a 5 V, determinare la piu' piccola tensione di comando in fase di Hold che garantisca un errore per iniezione di carica non superiore a 0.2 LSB.

- d) Determinare il minimo W/L che deve possedere il transistore MOS del circuito di Sample & Hold per garantire un tempo di  $Sample (T_{Sample})$  non superiore a 1 µs nel caso di segnali che coprono l'intera dinamica dell'ADC se l'errore massimo concesso e' di 0.2 LSB. Si assuma  $V_G$  pari a 5 V in fase di Sample.

- e) Nelle ipotesi che l'ADC sia basato su una logica ad approssimazioni successive (*SAR*), determinare la minima frequenza di *clock* richiesta per il suo corretto funzionamento, assumendo un tempo di *Hold* pari a 20 µs.