## Fondamenti di Elettronica - Ingegneria Elettronica -2007/08 Primo Appello – 29 febbraio 2008

Indicare chiaramente la domanda a cui si sta rispondendo. Ad esempio 1a) .... Risolvere obbligatoriamente i punti in grassetto.

## **Esercizio 1**

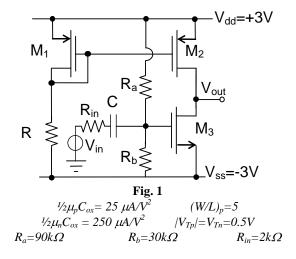

Si consideri il circuito amplificatore mostrato in Fig. 1

- a) Determinare il valore della resistenza R che garantisca una corrente di polarizzazione del transistore  $M_1$  pari a 0.5 mA ed il (W/L) del transistore  $M_3$  compatibile con la polarizzazione del circuito.

- b) Determinare il trasferimento di piccolo segnale  $v_{out}/vi_{in}$  a media frequenza (C circuito chiuso), assumendo per il transistore  $M_2$  una resistenza di uscita  $r_0$ =50k $\Omega$ .

- c) Dimensionare il valore che deve assumere la capacita' *C* perche' segnali sinusoidali di ingresso con frequenza pari a *1kHz* subiscano una attenuazione pari a 10 dB.

- d) Se all'alimentazione negativa  $V_{ss}$  e' sovrapposto un disturbo sinusoidale con frequenza pari a 100Hz e ampiezza pari a 100 mV, determinare l'ampiezza del disturbo risultante in uscita. (Si assuma il valore di capacita' determinato al punto c).

## Esercizio 2

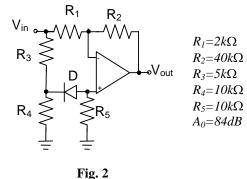

Si consideri il circuito contenente un amplificatore operazionale ed un diodo mostrato in Fig. 2. Per il diodo si assuma una tensione di accensione pari a 0.7V.

- a) Supponendo il diodo D spento, si determini l'espressione ed il valore del guadagno reale del circuito.

- b) Supponendo il diodo D acceso, si determini l'espressione ed il valore del guadagno ideale del circuito.

- c) Determinare il valore della tensione di ingresso  $V_{in}$  per cui si ha l'accensione del diodo.

- d) Sostituendo al diodo *D* una capacita' da *100pF*, determinare l'espressione ed il valore della costante di tempo da essa introdotta ad anello chiuso, nelle ipotesi di amplificatore operazionale ideale.

- e) Si supponga di dover campionare alla frequenza di 10 kHz un segnale e di digitalizzare il valore dei campioni mediante un ADC a doppia rampa a 12 bits di cui si copra l'intero Full Scale Range (FSR). Determinare la frequenza di clock da fornire all'ADC.

## Esercizio 3

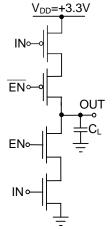

Si consideri il circuito logico mostrato in Fig. 3, in cui il segnale logico EN (ed il suo negato) possono assumere valore pari a 0V ('0' logico) o +3.3V ('1' logico)

- a) Determinare la funzione logica svolta dal circuito, scrivendone la tabella delle verita' e giustificando la risposta.

- b) Determinare il ritardo di propagazione di tale porta, giustificando le eventuali approssimazioni effettuate.

$$V_{Tn}=/V_{Tp}/=0.7^{\circ}$$

$k_{n}=330 \mu A/V^{2}$

$k_{p}=100 \mu A/V^{2}$

$C_{L}=1pF$

Fig. 3