# Fondamenti di Elettronica - Ingegneria Elettronica - a.a. 2018/19 2ª prova in itinere - 28 giugno 2019

- 1. Riportare sulla prima pagina del foglio protocollo nome, cognome, numero di matricola, data, "2ª prova in itinere", numero totale di fogli consegnati.

- 2. Numerare tutti i fogli e riportare su ciascuno almeno nome, cognome e numero di matricola.

- 3. Scrivere con grafia leggibile e con la penna.

- 4. Indicare chiaramente la domanda a cui si sta rispondendo. Ad esempio 1a)...

- 5. Risolvere per primi i punti in grassetto, perche' ritenuti piu' facili. La durata della prova e' 3 ore.

- 6. Non sono ammessi libri o appunti o altro materiale, eccetto la calcolatrice.

### **Esercizio 1**

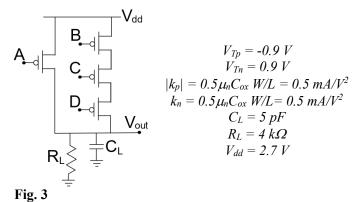

Si consideri il circuito riportato nella Fig. 1. Gli amplificatori operazionali saturino alle tensioni di alimentazione.  $V_b$  sia un generatore di tensione DC e  $V_{in}$  un generatore di segnale.

- a) Determinare l'espressione ed il valore del guadagno reale  $V_{out,1}/V_{in}$  a bassa frequenza se l'amplificatore operazionale I e' caratterizzato da un guadagno ad anello aperto  $A_{\theta,1} = 70 \ dB$ . Tracciare, quindi, il diagramma di Bode del modulo del trasferimento ideale  $V_{out,1}/V_{in}$ .

- b) Determinare l'espressione ed il valore delle soglie di scatto del Trigger di Schmitt ed il massimo valore *rms* del rumore sovrapposto al segnale in ingresso che non causi eccessive commutazioni spurie.

- c) Se entrambi gli amplificatori operazionali sono caratterizzati da una tensione di offset pari a 12 mV, determinarne quantitativamente l'effetto sul funzionamento del blocco amplificatore e del trigger di Schmitt.

- d) Determinare il minimo valore della corrente di uscita che deve poter fornire l'amplificatore operazionale *l* per non compromettere il funzionamento del circuito.

- e) Determinare il margine di fase del blocco amplificante se l'amplificatore operazionale l e' caratterizzato da un prodotto guadagno-larghezza di banda,  $GBWP = 50 \ MHz$ .

#### Esercizio 2

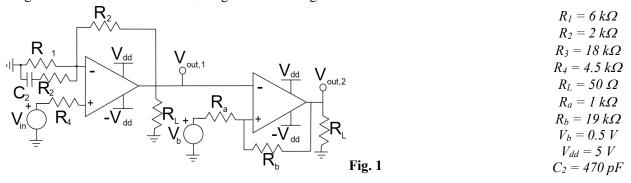

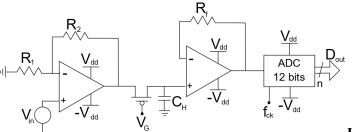

Si consideri la catena di acquisizione mostrata in Fig. 2, in cui  $V_{in}$  e' un generatore di segnali sinusoidali di ampiezza massima 200 mV e frequenza 200 kHz. Gli amplificatori operazionali saturino alle tensioni di alimentazione.

- a) Determinare la risoluzione ottenibile in ingresso espressa in mV. Quale sarebbe il valore ottimale della resistenza  $R_1$ ? Motivare la risposta.

- b) Determinare le tensioni di comando del gate del pMOS che garantiscano una resistenza  $R_{ds,on}$  minore di  $10 \Omega$  in fase di Sample e pMOS spento con 2 V di margine in fase di Hold.

- c) Assumendo una durata del tempo di *Sample* pari a  $T_{Sample} = 200 \text{ ns}$  e la frequenza di campionamento pari a 1 MHz, determinare il minimo valore che deve assumere la frequenza di clock,  $f_{ck}$ , dell'ADC, supposto ad approssimazioni successive, che sia compatibile con il corretto funzionamento della catena.

- d) Assumendo che gli amplificatori operazionali siano caratterizzati da un valore medio delle correnti di *bias* uscenti dall'amplificatore operazionale pari a  $I_B = 200 \text{ nA}$ , determinare quali valori puo' assumere la capacita' di *Hold*. Si assuma una tensione di comando al *gate* pari a  $V_G = -6 \text{ V}$  ed una frequenza di *clock* pari a 30 MHz.

- e) Determinare il minimo valore dello *Slew-Rate* che deve possedere il secondo amplificatore operazionale per non incorrere in limitazioni da *Slew-Rate*. Si assuma una capacita' di *Hold*  $C_H = 122 \ pF$  ed una tensione di comando al *gate* pari a  $V_G = -6 \ V$ .

## Fondamenti di Elettronica - Ingegneria Elettronica - a.a. 2018/19 Appello Zero - 28 giugno 2019

- 1. Riportare sulla prima pagina del foglio protocollo nome, cognome, numero di matricola, data, "Appello Zero", numero totale di fogli consegnati.

- 2. Numerare tutti i fogli e riportare su ciascuno almeno nome, cognome e numero di matricola.

- 3. Scrivere con grafia leggibile e con la penna.

- 4. Indicare chiaramente la domanda a cui si sta rispondendo. Ad esempio 1a)...

- 5. Risolvere per primi i punti in grassetto, perche' ritenuti piu' facili. La durata della prova e' 3 ore.

- 6. Non sono ammessi libri o appunti o altro materiale, eccetto la calcolatrice.

### Esercizio 1

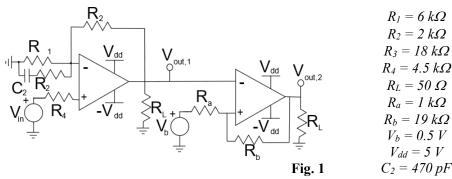

Si consideri il circuito riportato nella Fig. 1. Gli amplificatori operazionali saturino alle tensioni di alimentazione.  $V_b$  sia un generatore di tensione DC e  $V_{in}$  un generatore di segnale.

- a) Determinare l'espressione ed il valore del guadagno reale  $V_{out,1}/V_{in}$  a bassa frequenza se l'amplificatore operazionale I e' caratterizzato da un guadagno ad anello aperto  $A_{\theta,I} = 70~dB$ . Tracciare, quindi, il diagramma di Bode del modulo del trasferimento ideale  $V_{out,1}/V_{in}$ .

- b) Determinare l'espressione ed il valore delle soglie di scatto del Trigger di Schmitt ed il massimo valore *rms* del rumore sovrapposto al segnale in ingresso che non causi eccessive commutazioni spurie.

- c) Determinare il margine di fase del blocco amplificante se l'amplificatore operazionale l e' caratterizzato da un prodotto guadagno-larghezza di banda,  $GBWP = 50 \, MHz$ .

### Esercizio 2

Si consideri la catena di acquisizione mostrata in Fig. 2, in cui  $V_{in}$  e' un generatore di segnali sinusoidali di ampiezza massima 200 mV e frequenza 200 kHz. Gli amplificatori operazionali saturino alle tensioni di alimentazione.

- $V_{Tp} = -IV$   $|k_p| = 5 \text{ mA/V}^2$   $R_f = 100 \text{ k}\Omega$   $R_1 = 1 \text{ k}\Omega$   $R_2 = 9 \text{ k}\Omega$  $V_{dd} = 5 \text{ V}$

- Fig. 2

- a) Determinare la risoluzione ottenibile in ingresso espressa in mV. Quale sarebbe il valore ottimale della resistenza  $R_1$ . Motivare la risposta.

- b) Assumendo una durata del tempo di *Sample* pari a  $T_{Sample} = 200 \text{ ns}$  e la frequenza di campionamento pari a 1 MHz, determinare il minimo valore che deve assumere la frequenza di clock,  $f_{ck}$ , dell'ADC, supposto ad approssimazioni successive, che sia compatibile con il corretto funzionamento della catena.

- c) Assumendo che gli amplificatori operazionali siano caratterizzati da un valore medio delle correnti di *bias* uscenti dall'amplificatore operazionale pari a  $I_B = 200 \text{ nA}$ , determinare quali valori puo' assumere la capacita' di *Hold*. Si assuma una tensione di comando al *gate* pari a  $V_G = -6 \text{ V}$  ed una frequenza di *clock* pari a 30 MHz.

#### Esercizio 3

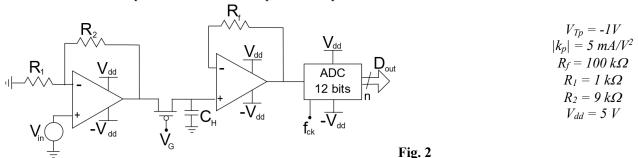

Si consideri il circuito a transistori mostrato in Fig. 3.

- a) Determinare la funzione logica svolta dalla porta ed il valore analogico della tensione di uscita  $V_{out}$  nel caso in cui A = B = C = D = 1 e nel caso in cui A = 0 e B = C = D = 1.

- b) Disegnare l'andamento temporale della tensione di uscita  $V_{out}$  a seguito della commutazione degli ingressi da A=I, B=C=0, D=1 a A=0, B=1, C=D=0, quotandone tutti i punti significativi.

- c) Disegnare la corrispondente porta logica in tecnologia *CMOS*, giustificando tutte le scelte effettuate.

- d) Determinare la massima ampiezza di un disturbo sulla alimentazione positiva che non faccia variare il valore analogico della tensione di uscita di piu' di  $V_{dd}/4$ . Si facciano le dovute approssimazioni.