## Fondamenti di Elettronica - Ingegneria Elettronica - a.a. 2011/12 secondo appello - 27 settembre 2012

Indicare chiaramente la domanda a cui si sta rispondendo. Ad esempio 1a) .... Risolvere per primi i punti in grassetto. La durata della prova e' 3 ore. Non sono ammessi libri o appunti o altro materiale, eccetto la calcolatrice.

## Esercizio 1

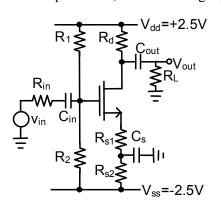

Si consideri lo stadio amplificatore, mostrato in Fig. 1, in cui  $v_{in}$  e' un generatore di tensione di piccolo segnale.

$C_{in} = 4.7 \mu F$   $C_{s} = 10 \mu F$   $C_{out} = 1 \mu F$   $R_{in} = 50 \Omega$   $R_{s2} = 1.5 k\Omega$   $R_{d} = 5 k\Omega$   $R_{L} = 10 k\Omega$   $R_{I} = R_{2} = 50 k\Omega$   $V_{Tn} = 1 V$   $V_{2}\mu_{n} C_{ox} = 100 \mu A/V^{2}$   $W = 3\mu m; L = 1\mu m$   $\mu_{p} = 400 \text{ cm}^{2}/(Vs); t_{ox} = 5nm$   $\varepsilon_{ox} = V_{3}\varepsilon_{Si} = V_{3}10^{-12}F/cm$

Fig. 1

- a. Determinare la polarizzazione del circuito, dimensionando la resistenza  $R_{sI}$  perche' nel transistore scorra una corrente  $I_D = 0.3 mA$ . Determinare, con il valore di polarizzazione ottenuto, il numero totale di elettroni nel canale del MOSFET.

- b. Se le resistenze fossero realizzate con un processo in grado di garantire una dose dell'impiantazione di Boro pari a  $D = 10^6 \mu m^{-2}$ , determinare il numero di quadri necessario per realizzare la resistenza  $R_{\rm s2}$ .

- c. Nelle ipotesi di  $r_0 = \infty$ , tracciare il diagramma di Bode del modulo del trasferimento  $v_{out}/v_{in}$ , quotandone tutti i punti significativi.

- d. Determinare la massima escursione positiva e negativa del nodo di *drain* che consenta al circuito di operare "correttamente" come amplificatore. Giustificare la risposta.

## Esercizio 2

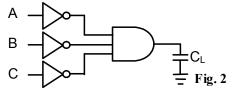

Si consideri il circuito logico mostrato in Fig.2, realizzato con porte logiche elementari alimentate a 3.3V.

- a. Determinare la funzione logica svolta dal circuito e disegnare la porta logica CMOS che svolga tale funzione, giustificando la risposta.

- b. Con riferimento alla porta logica CMOS progettata al punto a., determinare il massimo valore che puo' assumere la capacita'  $C_L$ , perche' il tempo di commutazione relativo a tutte le transizioni sia minore di 7 ns.

- c. Se la porta logica CMOS in questione pilotasse un inverter CMOS ad area minima in tecnologia  $0.18 \, \mu m$ , con spessore dell'ossido pari a  $3 \, nm$ , determinare la potenza dissipata dalla porta se gli ingressi sono cortocircuitati tra loro e pilotati alla frequenza di  $80 \, MHz$ .

$$k_n = \frac{1}{2}\mu_n C_{ox} (W/L)_n = 200 \ \mu A/V^2$$

$$|k_p| = \frac{1}{2}\mu_p C_{ox} (W/L)_p = 700 \ \mu A/V^2$$

$$V_{Tn} = |V_{Tp}| = 0.7V$$

$$\varepsilon_{ox} = \frac{1}{3}\varepsilon_{Si} = \frac{1}{3}10^{-12} F/cm$$

## Esercizio 3

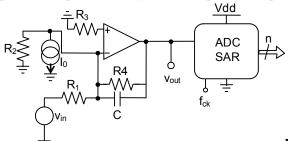

Si consideri la catena di acquisizione mostrata in Fig. 3 per la digitalizzazione di segnali di tensione di entrambe le polarita' (o positivi o negativi) di ampiezza compresa nell'intervallo  $\pm 100 \ mV$ .

$$V_{dd} = 5 V$$

$R_1 = 1 k\Omega$

$R_2 = 50 k\Omega$

$R_3 = R_1 // R_2 // R_3$

$R_4 = 12 k\Omega$

$C = 10 pF$

$f_{ck} = 10 MHz$

Fig. 3

- a. Determinare l'intervallo di valori ammessi per l'intensita' di corrente  $I_{\theta}$  per garantire la corretta digitalizzazione dei segnali, assumendo l'amplificatore operazionale ideale  $(A_{\theta} = \infty)$ .

- b. Determinare il margine di fase del circuito amplificatore, se l'amplificatore operazionale e' caratterizzato da un prodotto guadagno larghezza di banda GBWP = 80MHz.

- c. Determinare il numero massimo di bit che deve possedere l'ADC ad approssimazioni successive (SAR) per garantire di poter rispettare il criterio di Nyquist e per non commettere errori superiori ad 1 LSB, se il segnale di ingresso e' una sinusoide di ampiezza  $A = 100 \ mV$  e frequenza  $f = 100 \ kHz$ .