## Fondamenti di Elettronica - Ingegneria Elettronica - a.a. 2014/15 Quinto Appello 25 febbraio 2016

Indicare chiaramente la domanda a cui si sta rispondendo. Ad esempio 1a) .... Risolvere per primi i punti in grassetto. La durata della prova e' 3 ore. Non sono ammessi libri o appunti o altro materiale, eccetto la calcolatrice.

## Esercizio 1

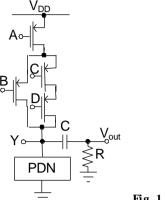

Si consideri la porta logica complessa mostrata in Fig. 1.

- Determinare la funzione logica svolta dalla porta, motivando la risposta. Disegnare, quindi, la rete di pull-down necessaria a completare la porta logica in Fig. 1, giustificando le scelte effettuate.

- Determinare il massimo valore della b. corrente che attraversa i transistori della rete di pull down, nelle ipotesi che il resistore R abbia resistenza nulla.

- Se A = B = C = D sono pilotati da un segnale di clock alla frequenza di 1 kHz, facendo disegnare, le dovute approssimazioni, l'andamento della tensione di ingresso, della tensione al nodo Y e della tensione di uscita  $V_{out}(t)$ , quotandone tutti i punti significativi.

$/V_{Tp}/=V_{Tn}=0.4V$  $^{1/2}\mu_{n} C_{ox} = 0.1 \text{ mA/V}^{2}$  $1/2\mu_p C_{ox} = 0.04 \text{ mA/V}^2$  $(\dot{W/L})_n=7$  $(W/L)_p = 10$ C = 8pF $R = 80 k\Omega$  $V_{dd} = 1.7 \ V$

Fig. 1

## Esercizio 2

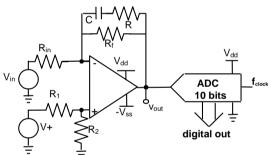

Si consideri il circuito mostrato in Fig. 2. Si assuma che l'amplificatore operazionale saturi alle trensioni di alimentazione.

$$R = 10 k\Omega$$

$$R_f = 100 k\Omega$$

$$R_1 = R_2 = 200 k\Omega$$

$$R_{in} = 2.5 k\Omega$$

$$C = 470 nF$$

$$V_{dd} = V_{ss} = 5 V$$

Fig.2

- Determinare il guadagno ideale di tensione  $V_{out}/V_{in}$  ad alta e a bassa frequenza, assumendo  $V^+ = 0$  V.

- Determinare l'intervallo di valori della tensione V<sup>+</sup> che consenta di mantenere in dinamica per l'ADC una sinusoide di ampiezza A = 100 mV e frequenza f = 20 kHz.

- Determinare il minimo valore che deve possedere la frequenza di clock,  $f_{clock}$ , dell'ADC, supposto ad approssimazioni successive, per poter correttamente convertire, garantendo un errore non superiore a 0.3LSB, la sinusoide di cui al punto b.

- Determinare il margine di fase del circuito amplificatore, nelle ipotesi che l'amplificatore operazionale sia caratterizzato da un prodotto guadagno larghezza di banda GBWP = 80 MHz e valutare la stabilita' del circuito.

## Esercizio 3

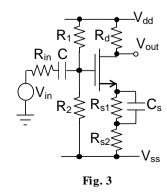

Si consideri il circuito amplificatore mostrato in Fig. 3.

- Calcolare la polarizzazione del circuito (correnti in tutti i rami e tensioni a tutti i nodi).

- Determinare il trasferimento di piccolo segnale  $V_{out}/V_{in}$  ad alta frequenza, nelle ipotesi che il transistore sia caratterizzato da una resistenza di uscita infinita.

- Tracciare, quotandone tutti i punti significativi, l'andamento del diagramma di Bode del modulo della funzione di trasferimento  $V_{out}(s)/V_{in}(s)$ , nelle ipotesi che il transistore sia caratterizzato da una resistenza di uscita infinita.

$R_{in} = 1k \Omega$  $R_d = 5 k\Omega$  $R_1 = 480k\Omega$  $R_2=520k\Omega$  $R_{s1} = 3 k\Omega$  $R_{s2} = 0.5 k\Omega$  $C = 470 \; nF$  $C_s=1\mu F$  $V_{dd} = 5 V$  $V_{ss} = -5 V$  $k_n = \frac{1}{2} \mu_n C_{ox}(W/L)_n = 1 \text{ mA/V}^2$  $V_{Tn} = 0.7 V$