# Fondamenti di Elettronica - Ingegneria Elettronica - a.a. 2013/14 Primo Appello - 15 luglio 2014

Indicare chiaramente la domanda a cui si sta rispondendo. Ad esempio 1a) .... Risolvere per primi i punti in grassetto. La durata della prova e' 3 ore. Non sono ammessi libri o appunti o altro materiale, eccetto la calcolatrice.

## **Esercizio 1**

Si consideri la funzione logica  $Y = \overline{A} \cdot \overline{B + C} \cdot \overline{A + D}$ .

- a. Disegnare la porta logica in forma minima, in una tecnologia CMOS caratterizzata da una tensione di alimentazione pari a  $V_{DD}=3.3~V$ , una tensione di soglia per i transistori  $V_{Tn}=/V_{Tp}/=0.7~V$ , un fattore  $\mu_n$   $C_{ox}=70\mu A/V^2$  e  $\mu_p$   $C_{ox}=25\mu A/V^2$ , una minima lunghezza di gate pari a  $0.25\mu m$ , che implementi tale funzione logica. Si giustifichino le scelte effettuate.

- b. Determinare il massimo valore che puo' assumere la capacita' di carico posta in uscita dalla porta progettata al punto a. verso massa perche' il massimo tempo di propagazione sia sempre minore di 8 ns, se si assume che la porta sia progettata ad area minima.

#### Esercizio 2

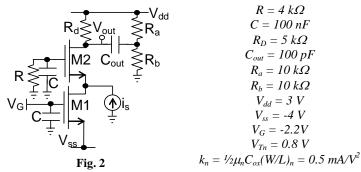

Si consideri il circuito amplificatore a MOSFET mostrato in Fig. 2, in cui  $i_s$  e' un generatore di corrente di piccolo segnale.

- a. Determinare la polarizzazione del circuito (tensioni a tutti i nodi e correnti in tutti i rami).

- b. Determinare il trasferimento di piccolo segnale  $v_{out}/i_s$  a media frequenza (C circuito chiuso e  $C_{out}$  circuito aperto), assumendo che tutti i transistori siano caratterizzati da una resistenza di uscita  $r_0 = \infty$

- c. Tracciare il diagramma di Bode del modulo del trasferimento di piccolo segnale  $v_{out}/i_s$ , assumendo che il transistore M1 sia caratterizzato da una resistenza di uscita  $r_{01} = 30 \text{ k}\Omega$ .

### Esercizio 3

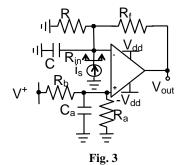

Si consideri il circuito amplificatore mostrato in Fig. 3, in cui  $i_s$  e' un generatore di corrente di segnale. Si supponga che l'amplificatore operazionale saturi alle tensioni di alimentazione.

- a. Tracciare in un diagramma temporale, quotandone tutti i punti significativi, l'andamento  $\underline{complessivo}$  di  $V_{out}(t)$ , quando in ingresso e' applicato un gradino di corrente positivo di ampiezza  $I\mu A$ . Si supponga l'amplificatore operazionale ideale.

- b. Determinare il margine di fase del circuito se l'amplificatore operazionale e' caratterizzato da un prodotto guadagno larghezza di banda pari a *GBWP=50MHz* e commentare il grado di stabilita' del circuito.

- c. Determinare il valore della resistenza di ingresso  $R_{in}$  indicata in Fig. 4 a bassa frequenza, se l'amplificatore operazionale e' caratterizzato da un guadagno ad anello aperto  $A_0 = 70dB$ .

$$\begin{array}{ll} R_a = 100 \ k\Omega & R_b = 200 \ k\Omega \\ C = 4 \ pF & C_a = 47 \ nF \\ R_f = 1 \ M\Omega & R = 100 \ k\Omega \\ V_+ = 300 \ mV & V_{dd} = +6V \end{array}$$

## Esercizio 4

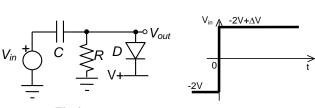

Si consideri il circuito mostrato in Fig. 4, contenente un diodo. Il diodo conduce quando e' polarizzato in diretta con una tensione ai suoi capi pari a 0.7 V. L'andamento temporale della tensione  $V_{in}$  e' riportato in Fig. 4b.

- a. Disegnare l'andamento temporale della tensione di uscita  $V_{oud}(t)$ , quotandone tutti i punti significativi e giustificando la risposta, se l'ampiezza  $\Delta V$  del gradino applicato in ingresso e' pari a 0.5V.

- b. Disegnare l'andamento temporale della tensione di uscita  $V_{out}(t)$ , quotandone tutti i punti significativi e giustificando la risposta, se l'ampiezza  $\Delta V$  del gradino applicato in ingresso e' pari a 4V.

Fig.4a  $V^{+} = +2 V \qquad R = 2 k\Omega$  C = 2.2 nF

Fig. 4b