## Fondamenti di Elettronica - Ingegneria Elettronica - 2005/06 2<sup>a</sup> prova in itinere – 13 febbraio 2006

Indicare chiaramente la domanda a cui si sta rispondendo. Ad esempio 1a) .... Risolvere obbligatoriamente i punti in grassetto

## Esercizio 1

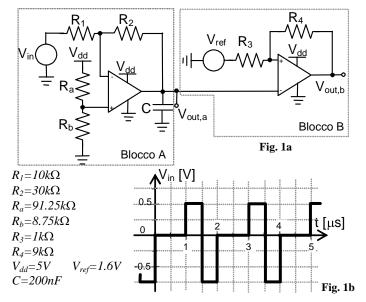

Si consideri il circuito riportato nella Fig. 1a.

- a) Disegnare la caratteristica di trasferimento ingresso-uscita del blocco A e del blocco B, quotandone tutti i punti significativi. (Si assuma che l'uscita degli amplificatori operazionali saturi alle tensioni di alimentazione e che gli amplificatori operazionali siano ideali).

- b) Disegnare in un diagramma temporale, quotandone tutti i punti significativi, l'andamento delle tensioni di uscita  $V_{out,a}$  e  $V_{out,b}$  quando il segnale in ingresso e' quello riportato in Fig. 1b. (Si assuma che gli amplificatori operazionali siano ideali).

- c) Se l'amplificatore operazionale del blocco A e' caratterizzato da una resistenza di uscita pari a  $r_{out}=1k\Omega$  e da un guadagno ad anello aperto  $A_0=72$  dB, disegnare in un diagramma temporale, quotandone tutti i punti significativi, il nuovo andamento delle tensioni di uscita  $V_{out,a}$  e  $V_{out,b}$ .

## Esercizio 2

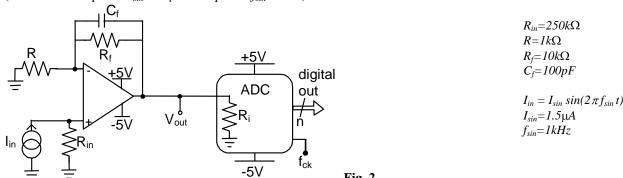

Si consideri il circuito, riportato nella Fig. 2, per la conversione mediante un convertitore analogico digitale del segnale  $I_{in}$  (sinusoide di ampiezza  $I_{sin}=1.5\mu A$  e frequenza  $f_{sin}=1kHz$ ).

- a) Determinare il trasferimento ideale  $V_{out}/I_{in}$  a bassa frequenza ( $C_f$  circuito aperto).

- b) Disegnare il diagramma di Bode del modulo del trasferimento ideale  $V_{out}/I_{in}$ , quotandone tutti i punti significativi.

- c) Determinare il numero di bit minimo richiesto all'ADC per garantire una risoluzione del 5‰ sul segnale di corrente applicato in ingresso.

- d) Dimensionare il valore della resistenza  $R_x$  da introdurre nel circuito per minimizzare l'effetto delle correnti di bias senza variare il guadagno dello stadio. Giustificare la risposta e specificare dove vada inserita la resistenza  $R_x$ .

- e) Se l'ADC e' caratterizzato da una resistenza di ingresso finita  $R_i$ , determinare il minimo valore che puo' assumere tale resistenza nel caso in cui l'amplificatore operazionale sia caratterizzato da una corrente di uscita massima pari a 5mA.

- f) Determinare la massima ampiezza che puo' assumere una componente spuria sovrapposta al segnale, supposta sinusoidale di frequenza  $f=20 \, MHz$ , per pesare meno di  $1 \, LSB$  (Si consideri ideale l'amplificatore operazionale).

- g) Determinare il valore di prodotto guadagno-banda (GBWP) richiesto perche' il polo ad anello chiuso dovuto all'amplificatore operazionale sia situato a 100 MHz.

- h) Determinare la frequenza di clock da fornire all'ADC, nel caso sia del tipo a gradinata e nel caso sia del tipo ad approssimazioni successive, per garantire un numero di campioni minimo pari a 9 entro ogni periodo della sinusoide. Si assuma che l'errore massimo ammesso per ogni campione sia pari a 1 LSB.