## Fondamenti di Elettronica - Ingegneria Elettronica - a.a. 2010/11 Secondo appello - 8 settembre 2011 Traccia di soluzione

### Esercizio 1

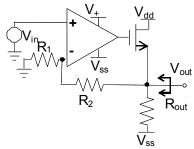

a) valore della resistenza  $R_s$  per garantire una corrente l=20mA, quando  $v_{in}$  e' pari a 0V

Con  $v_{in}$ =0V, la tensione al morsetto meno dell'amplificatore operazionale e' pari a 0V, pertanto in  $R_1$  non circola corrente e, quindi, neppure in  $R_2$ , quindi il *source* dell'nMOS si trova a 0V.

$$R_S = \frac{|V_{ss}|}{I} = 400\Omega$$

b) minimo valore della tensione  $V_{dd}$  che garantisca la saturazione del MOSFET, quando  $v_{in}$ =0V

Se nel transistore circolano 20 mA di corrente di polarizzazione, la tensione  $V_{GS}$  deve soddisfare la seguente relazione:

$$V_{GS} = V_{Tn} + \sqrt{\frac{I}{k_n}} = +2V$$

Quindi, poiche'  $V_S=0V$ ,  $V_G=+2V$ .

La condizione di saturazione richiede

$$V_{GD} < V_{Tn}$$

da cui si ricava che la minima tensione di alimentazione positiva, in assenza di segnale, e' di +1V.

c) espressione e valore del guadagno ideale  $v_{out}/v_{in}$

Il circuito e' retro azionato negativamente. Nelle ipotesi di retroazione ideale, la tensione al morsetto piu' dell'amplificatore operazionale si riporta al morsetto meno e fa fluire in R<sub>1</sub> una corrente

$$i = \frac{v_{in}}{R_1}$$

che scorrera' tutta in R<sub>2</sub>. Pertanto il guadagno ideale avra' la seguente espressione:

$$G_{id} = 1 + \frac{R_2}{R_1} = 11$$

come in una normale configurazione invertente.

### d) espressione e valore della resistenza di uscita Rout

Il circuito e' retro azionato negativamente. La retroazione idealmente tende ad annullare la resistenza  $R_{out}$ . Infatti se, spenti i generatori forzanti, applichiamo in uscita un generatore di prova di corrente – per non ostacolare l'effetto della retroazione –, la corrente iniettata si suddividerebbe, in assenza di retroazione tra il transistore ( $1/g_m$ ), la resistenza  $R_s$  ed il ramo di retroazione, causando un innalzamento della tensione di source del transistore. La frazione di corrente iniettata nel ramo di retroazione provocherebbe un innalzamento della tensione del morsetto meno dell'amplificatore operazionale, che a sua volta provocherebbe un abbassamento della tensione del nodo di uscita dell'amplificatore operazionale e, conseguentemente, del source del transistore, tendendo, quindi, a stabilizzare la tensione del nodo di uscita e, quindi, ad abbassare l'impedenza vista al nodo, rispetto a quella vista in assenza di retroazione.

$$R_{out} = \frac{R_{out}^{0}}{1 - G_{loop}^{*}(0)}$$

$$R_{out}^{0} = R_{S} / \frac{1}{g_{m}} / (R_{1} + R_{2}) \cong \frac{1}{g_{m}} = 25\Omega$$

$$R_{out} = 2.9m\Omega$$

e) tempo necessario perche' la tensione di uscita raggiunga il valore a regime, a meno dell'1%

Assumiamo un comportamento a singolo polo. Dobbiamo calcolare la posizione del polo ad anello chiuso e poi determinare la relazione tra la costante di tempo di tale polo ed il tempo necessario perche' la tensione di uscita raggiunga il valore a regime, a meno dell'1%. Imponendo

$$0.99 = 1 - \exp(-t/\tau)$$

$t = 4.6\tau$

Per il calcolo del polo ad anello chiuso procediamo graficamente.

$$G_{\text{loop}}(s) = -\frac{R_s //(R_1 + R_2)}{R_s //(R_1 + R_2) + \frac{1}{g_m}} \frac{R_1}{R_1 + R_2} \frac{A_0}{1 + s \tau_0}$$

da cui

$$G_{\text{and}}(s) = -G_{\text{id}}G_{\text{loop}}(s) = \left(1 + \frac{R_1}{R_2}\right) \frac{R_s //(R_1 + R_2)}{R_s //(R_1 + R_2) + \frac{1}{g_m}} \frac{R_1}{R_1 + R_2} \frac{A_0}{1 + s \tau_0} = \frac{R_s //(R_1 + R_2)}{R_s //(R_1 + R_2) + \frac{1}{g_m}} \frac{A_0}{1 + s \tau_0}$$

Pur non conoscendo il valore di  $A_0$  e  $\tau_0$  separatamente, possiamo ricavare che il modulo del guadagno d'andata taglia l'asse 0dB alla frequenza

$$|G_{\text{and}}(j\omega)| = 1 \Leftrightarrow f = A_0 f_0 \frac{R_s //(R_1 + R_2)}{R_s //(R_1 + R_2) + \frac{1}{g_m}} = 94MHz$$

da cui la frequenza a cui si ha l'incontro tra il modulo del guadagno ideale e il modulo del guadagno di andata e' pari a

$$f_{polo} = \frac{94MHz}{|G_{id}|} = 8.54MHz \Rightarrow \tau = 18.6ns$$

da cui ricaviamo che il tempo necessario perche' la tensione di uscita raggiunga il valore a regime, a meno dell'1% e' pari a 86ns.

## f) massima ampiezza di $v_{in}$ , sinusoidale, amplificato senza distorsioni

La massima escursione negativa del nodo di uscita si ha per lo spegnimento dell'nMOS. Quindi  $V_{out,neg}$ =-8V. In tali circostanze la tensione di uscita dell'amplificatore operazionale sara' tale che  $V_{GS}$ = $V_{Tn}$ , pertanto  $V_{G}$ =-7V, valore che puo' essere tranquillamente raggiunto. Da cui  $v_{in,neg}$ =-0.727.

Sulla dinamica positiva, il rischio e' che il transistore esca dalla zona di saturazione. Cio' accade quando  $V_{gd} = V_{Tn}$

da cui  $V_g = v_{Tn} + V_{dd} = 11V$ , valore che puo' essere raggiunto, dato che l'amplificatore operazionale satura alle tensioni di alimentazione.

Con tale tensione di gate, possiamo ricavare la corrente circolante nel transistore, mediante il sistema

da cui  $V_{GS}$ =2.44V,  $V_{out.pos}$ =+8.56V e  $V_{in.max}$ =0.778V.

Pertanto la condizione limitante si ha per l'ansa negativa e la massima ampiezza della sinusoide in ingresso e' 727mV.

# g) In presenza di un disturbo sinusoidale di ampiezza 100 mV, sovrapposto all'alimentazione $V_{\rm ss}$ , ampiezza del segnale di uscita $v_{out}$

Per semplicita' calcolo l'equivalente Thevenin, visto dal source del transistore in assenza di  $R_S$ . In analogia con il ragionamento del d), la resistenza equivalente e' data da

$$R^* = \frac{R_{eq}^0}{1 - \widetilde{G}_{loop}(0)}$$

$$R_{eq}^0 = \frac{1}{g_m} / / (R_1 + R_2) \cong \frac{1}{g_m} = 25\Omega$$

$$\widetilde{G}_{loop}(0) = -\frac{(R_1 + R_2)}{(R_1 + R_2) + \frac{1}{g_m}} \frac{R_1}{R_1 + R_2} A_0 = -9.087 \times 10^3$$

$R_{eq} = 2.75 m\Omega$

Questa strada si avvale dell'ipotesi di poter considerare il disturbo un piccolo segnale per il transistore.

$$v_{out,dist} = \frac{R_{eq}}{R_{eq} + R_S} v_{dist} = 0.69 \mu V!!!!$$

### Esercizio 2

#### a) soglia logica di commutazione dell'inverter CMOS

Per calcolare la soglia logica di commutazione, imponiamo l'uguaglianza delle correnti di saturazione

$$\begin{split} I_{n} &= \left| I_{p} \right| \\ k_{n} \left( V_{GS,n} - V_{T,n} \right)^{2} &= \left| k_{p} \right| \left( V_{GS,p} - V_{T,p} \right)^{2} \\ \sqrt{k_{n}} \left( V_{in} - V_{T} \right) &= \sqrt{\left| k_{p} \right|} \left( V_{dd} - V_{T} - V_{in} \right) \end{split}$$

da cui si ricava

$$V_{IN,TH} = \frac{\left[\sqrt{k_n} - \sqrt{|k_p|}\right] V_T + \sqrt{|k_p|} V_{dd}}{\sqrt{k_n} + \sqrt{|k_p|}} = 1.504V$$

correttamente minore di  $V_{dd}/2$ , visti i valori relativi dei fattori di trans conduttanza dei due MOSFET.

b) tempo necessario perche' la tensione di uscita  $v_{out}$  transisca dal 100% al 40% del suo valore Nella transizione alto-basso dell'uscita, agisce l'nMOS che garantisce la scarica della capacita', operando dapprima in zona di saturazione e, poi, in zona ohmica. Per non fare conti complicati, possiamo ricorrere all'approssimazione ohmica o a quella satura (e' sufficiente uno solo dei due approcci).

Approssimazione ohmica

Calcoliamo il valore della  $R_{ds,on}$ , del transistore nMOS:

$$R_{ds,on} = \frac{\partial V_{DS}}{\partial I_D}\bigg|_{V_{DS} = 0} = \frac{1}{2k_n(V_{GS} - V_T)} = 1k\Omega$$

Occorre calcolare, ora, il tempo necessario perche' la tensione di uscita  $v_{out}$  transisca dal 100% al 40% del suo valore.

$$\begin{aligned} &V_{out} = V_{DD} \exp \left(-\frac{t}{\tau}\right) \\ &\tau = R_{ds,on}C \\ &V_{out} = V_{DD} \Rightarrow t = 0 \\ &V_{out} = 0.4V_{DD} \Rightarrow t = 0.916\tau \end{aligned}$$

da cui

$$t_{HL_{100\%-40\%}}=0.916\tau=0.46ns$$

Approssimazione satura

$$t_{HL_{100\%-40\%}} = \frac{Q_{100\%} - Q_{40\%}}{I_{D,n,sat}} = \frac{0.6CV_{dd}}{k_n (V_{dd} - V_T)^2} = 0.792 ns$$

### c) minima ampiezza segnale di ingresso $v_{in}$ in grado di accendere il diodo D.

Perche' il diodo D si accenda, la tensione ai suoi capi deve essere maggiore di 0.7V, con la corretta polarita'. Questo implica la seguente disuguaglianza, in cui chiamiamo  $V_{out,1}$  la tensione in ingresso all'inverter:

$$V_{out,1} - V_L > 0.7V$$

ma, fintantoche' il diodo D e' spento, nella resistenza R non circola corrente e, pertanto,  $V_{out,1}=V_{in}$ . Da qui si ricava che la minima tesnione di ingresso necessaria per accendere il diodo D e':

$$V_{in} > 0.7V + V_L = 1.2V$$

Poiche' il valore di tale tensione e' inferiore alla soglia logica di commutazione dell'inverter, calcolata al punto a), l'inverter non commuta con tale ampiezza del gradino di tensione di ingresso.

La minima ampiezza per cui si avrebbe la commutazione dell'uscita e' superiore alla soglia logica di commutazione dell'inverter.