## Fondamenti di Elettronica - Ingegneria Elettronica -2005/06 Appello del 7 marzo 2006

Indicare chiaramente la domanda cui si sta rispondendo. Ad esempio 1a) .... Risolvere obbligatoriamente i punti in grassetto.

## **Esercizio 1**

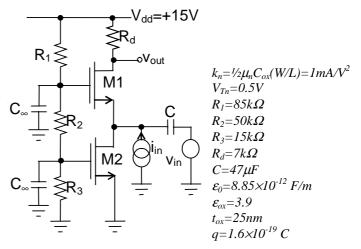

Si consideri il circuito a *MOSFET* riportato nella Fig. 1, nel quale  $i_{in}$  e' un generatore di corrente di segnale e  $v_{in}$  un generatore di tensione di segnale.

- a) Determinare le tensioni a tutti i nodi e le correnti in tutti i rami.

- b) Determinare il trasferimento di piccolo segnale  $v_{out}/v_{in}$  a media frequenza (C circuito chiuso).

- c) Determinare il trasferimento di piccolo segnale  $v_{out}/i_{in}$  a bassa frequenza (C aperta), assumendo per il solo transistore M2 una tensione di Early  $|V_A|$ =75V.

- d) Disegnare il diagramma di Bode del modulo del trasferimento  $v_{out}/v_{in}$  e del trasferimento  $v_{out}/i_{in}$ , quotandone tutti i punti significativi (transistore M2 tensione di Early  $|V_A|$ =75V).

- e) Determinare il numero di elettroni immagazzinati nel canale del transistore M1, quando e' polarizzato con una tensione  $V_{GS}$  pari a quella calcolata al punto a) ed una tensione  $V_{DS}=0V$ , assumendo che la larghezza di canale sia  $W=48\mu m$  e la lunghezza  $L=4\mu m$ .

Fig. 1

## Esercizio 2

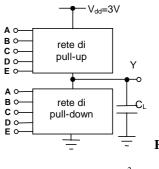

Si consideri la porta logica in tecnologia CMOS mostrata in Fig. 2, che svolge la funzione logica  $Y = \overline{|(A \cdot B) + (C \cdot D)| \cdot E}$ .

- a) Disegnare la rete di *pull-up* e la rete di *pull-down*, giustificando le scelte effettuate.

- b) Assumendo che tutti i transistori della porta siano caratterizzati dal medesimo fattore di forma (W/L), si determini il valore di fattore di forma necessario per garantire un tempo di propagazione pari a 10ns nella transizione degli ingressi:  $10101 \Rightarrow 00111$

- c) Se si realizzasse la medesima porta logica in una tecnologia CMOS caratterizzata da tensione di alimentazione dimezzata, tensione di soglia dimezzata e spessore dell'ossido dimezzato, mantenendo i medesimi fattori di forma per i transistori, determinare come varia il ritardo di propagazione, nel caso piu' gravoso.

Fig. 2

$$\frac{1}{2} \cdot \mu_n C_{ox} = 0.4 \text{mA/V}^2$$

$\frac{1}{2} \cdot \mu_p C_{ox} = 0.16 \text{mA/V}^2$

$\frac{1}{2} \cdot \mu_p C_{ox} = 0.8 \text{V}$

$\frac{1}{2} \cdot \mu_p C_{ox} = 0.8 \text{V}$

$\frac{1}{2} \cdot \mu_p C_{ox} = 0.8 \text{V}$

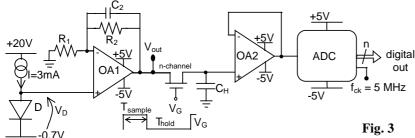

## Esercizio 3

a)

Si consideri il circuito riportato nella Fig. 3, che sfrutta la dipendenza dalla temperatura della tensione ai capi di una giunzione pn (-1.8mV/°C) per misurare la temperatura. Si assuma  $V_D$ =0.7V per una temperatura di 0°C.

$$R_1=1k\Omega$$

$R_2=30k\Omega$

$C_2=10pF$

$V_T=1.2V$

$k_n=\frac{1}{2}\mu_nC_{ox}(W/L)=5mA/V$

$C_H=10nF$

- Scrivere l'espressione della tensione di uscita  $V_{out}$  in funzione della temperatura a bassa frequenza.

- b) Determinare il numero minimo di bit dell'ADC necessario per garantire una risoluzione di ±0.5°C.

- Determinare l'errore dovuto al *droop* (espresso in LSB) se l'amplificatore operazionale 2 e' caratterizzato da una corrente di *bias*  $I_b = 500nA$  e la fase di Hold ha una durata pari a  $T_{hold}=18\mu s$ .

- d) Determinare la tensione di comando  $V_G$  da applicare al *gate* dell'interruttore  $\dot{N}MOS$  per garantire una resistenza virtualmente infinita durante la fase di Hold ed una resistenza non superiore a  $R_{ds,on}=10\Omega$  nella fase di Sample se la temperatura varia nell'intervallo  $\pm 50$ °C.

- e) Determinare per via grafica l'andamento in frequenza del trasferimento reale  $V_{out}/V_D$  se l'amplificatore operazionale 1 e' caratterizzato da GBWP=30MHz.