## Fondamenti di Elettronica - Ingegneria Elettronica - a.a. 2015/16 2<sup>a</sup> prova in itinere - 4 luglio 2016

Indicare chiaramente la domanda a cui si sta rispondendo. Ad esempio 1a) .... Risolvere per primi i punti in grassetto. La durata della prova e' 3 ore. Non sono ammessi libri o appunti o altro materiale, eccetto la calcolatrice.

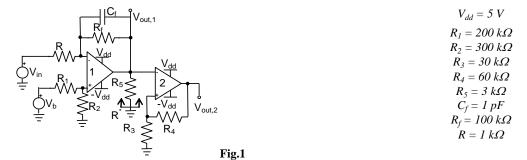

## Esercizio 1

Si consideri il circuito mostrato in Fig. 1. Si assuma che gli amplificatori operazionali saturino alle tensioni di alimentazione.

- a. Determinare l'espressione della tensione di uscita  $V_{out,I}$  in funzione di  $V_{in}$  e di  $V_b$ , a bassa frequenza, nelle ipotesi che l'amplificatore operazionale sia caratterizzato da un guadagno ad anello aperto in continua pari a  $A_0 = 80 \ dB$ .

- b.Determinare l'ampiezza del ciclo di isteresi ed il valore medio delle soglie di scatto relativamente al circuito comparatore, mostrando in dettaglio i calcoli effettuati per determinare tali valori. Determinare, inoltre, il massimo valore r.m.s. del rumore sovrapposto al segnale di ingresso  $V_{in}$  che non causi commutazioni spurie. Si assumano gli amplificatori operazionali ideali e  $C_f$  un circuito aperto, si facciano le eventuali approssimazioni necessarie, motivandole.

- c. Se il secondo amplificatore operazionale e' caratterizzato da un valor medio della corrente di bias  $I_{bias} = 20 \text{ nA}$  (uscente dai morsetti dell'operazionale), e da un offset delle correnti di bias pari a I nA, determinarne l'effetto sull'ampiezza del ciclo di steresi e sul valor medio delle soglie di scatto.

- d. Calcolare l'espressione ed il valore della resistenza  $R^*$  se l'amplificatore operazionale 1 e' caratterizzato da un guadagno ad anello aperto  $A_0 = 80 \ dB$  e da una resistenza di uscita  $r_{out} = 480 \ \Omega$ .

- e. Con riferimento all'amplificatore operazionale 1, determinare l'intervallo di frequenze entro le quali il guadagno reale puo' essere considerato, con buona approssimazione, coincidente con il guadagno ideale, se l'amplificatore operazionale 1 e' caratterizzato da un prodotto guadagno larghezza di banda *GBWP* = 60 *MHz*.

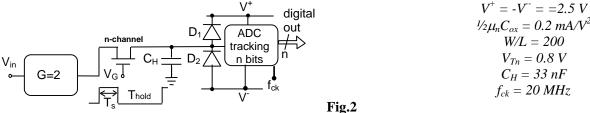

## Esercizio 2

Si consideri la catena di acquisizione mostrata nella Fig. 2, in cui  $V_{in}$  e' un generatore di tensione. Si assuma per i diodi  $D_1$  e  $D_2$  una tensione di accensione pari a 0.7V. I segnali di ingresso sono dei rettangoli con ampiezze comprese nell'intervallo (-200 mV, +200 mV) e durata  $8 \mu s$ .

- a. Determinare il numero di bit che l'ADC deve possedere per garantire una risoluzione dell'1% sui segnali in ingresso. Determinare quindi il valore di 1 LSB riferito all'ingresso.

- b. Determinare la minima tensione di comando da applicare al *gate* del transistore del circuito di *Sample & Hold* che garantisca che il minimo tempo di *Sample* per avere errori minori dell'1% sia inferiore a *100 ns*.

- c. Se l'ADC fosse a 10 bits, dopo quanto tempo dal fronte di salita del rettangolo, il dato in uscita dall'ADC e' valido? Si assuma la minima durata del tempo di Hold, compatibile con il funzionamento della catena e si trascuri la durata del tempo di Sample, ipotizzando il transistore MOS un interruttore ideale.

- d. Assumendo che il convertitore, supposto a 10 bit, sia caratterizzato da un rapporto segnale rumore (SNR) pari a 57 dB, determinare la minima differenza di ampiezza dei segnali rettangolari in ingresso che puo' essere distinta. Motivare la risposta.

- e. Nelle ipotesi che l'ADC sia a 10 bits e assumendo un tempo di Hold pari al tempo di conversione massimo, determinare la massima corrente inversa dei due diodi supposti identici che garantisca un errore inferiore a LSB/8.