## Fondamenti di Elettronica - Ingegneria Elettronica - a.a. 2022/23 Terzo Appello- 23 gennaio 2024

- 1. Riportare sulla prima pagina del foglio protocollo nome, cognome, numero di matricola, cod. persona. data, "Terzo Appello", numero totale di fogli consegnati.

- 2. Numerare tutti i fogli e riportare su ciascuno almeno nome, cognome, numero di matricola, cod. persona.

- 3. Scrivere con grafia leggibile e con la penna

- 4. Indicare chiaramente la domanda a cui si sta rispondendo. Ad esempio 1a)...

- 5. Risolvere per primi i punti in grassetto, perche' ritenuti piu' facili. La durata della prova e' 2.5 ore.

- 6. Non sono ammessi libri o appunti o altro materiale, eccetto la calcolatrice.

## Esercizio 1

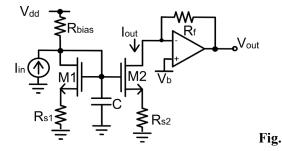

Si consideri il circuito a MOSFET riportato nella Fig. 1, in cui  $i_{in}$  e' un generatore di corrente di piccolo segnale. Si assuma l'amplificatore operazionale ideale.

- a) Determinare il minimo valore di  $V_b$  necessario per il corretto funzionamento dello specchio di corrente nonche' la polarizzazione del circuito (tensioni a tutti i nodi e correnti in tuti i rami).

- b) Determinare l'espressione del trasferimento  $V_{out}/i_{in}$  a bassa frequenza.

- c) Tracciare il diagramma di Bode del modulo del guadagno di corrente di piccolo segnale  $i_{out}/i_{in}$ . quotandone tutti i punti significativi,

- d) Determinare il minimo numero di quadri necessario per la resistenza  $R_{bias}$ , assumendo di disporre, per la realizzazione delle resistenze di un processo di impiantazione di Boro con dose  $D=1\times10^{13}~cm^{-2}$  oppure di un processo di impiantazione di Arsenico con dose  $D=8\times10^{12}~cm^{-2}$ .

$V_{dd} = +4.5 \ V$   $V_{Tn} = IV$   $\frac{1}{2}\mu_n C_{ox} = 100 \ \mu A/V^2$   $(W/L)_{n1} = 5$   $(W/L)_{n2} = 10$   $r_0 = \infty$   $R_{bias} = 4 \ k\Omega$   $R_{s1} = 1 \ k\Omega$   $R_{s2} = 500 \ \Omega$   $C = 41 \ pF$   $R_f = 700 \ \Omega$   $\mu_n = 1350 \ cm^2/(Vs)$   $\mu_p = 430 \ cm^2/(Vs)$

## Esercizio 2

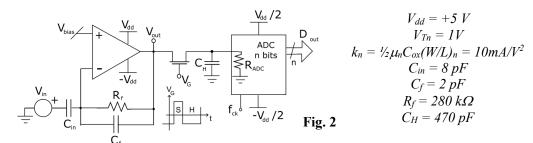

Si consideri la catena di acquisizione mostrata in Fig. 2. Gli amplificatori operazionali saturino alle tensioni di alimentazione. L'ADC sia del tipo a doppia rampa.

- a) Tracciare l'andamento temporale della tensione di uscita  $v_{out}(t)$ , quotandone tutti i punti significativi, nelle ipotesi di amplificatore operazionale ideale e assumendo un segnale di ingresso a gradino positivo di ampiezza A = 90mV.

- b) Determinare il valore di  $V_{bias}$  ed il numero di bit n dell'ADC richiesti per garantire una risoluzione di  $100 \ \mu V$  per un segnale di ingresso in grado di fornire alla uscita  $V_{out}$  un segnale di ampiezza  $0.9 \times V_{dd}$ .

- c) Determinare il margine di fase dello stadio amplificatore se l'amplificatore operazionale e' caratterizzato da un prodotto guadagno-larghezza di banda, GBWP = 30 MHz (Ao non e' noto separatamente).

- d) Assumendo ora un segnale di ingresso sinusoidale di massima ampiezza compatibile con il funzionamento del circuito e frequenza 10 kHz e la relativa  $V_{bias}$  necessaria, determinare la minima frequenza di clock richiesta per la corretta conversione, se l'ADC presenta una resistenza di ingresso  $R_{ADC} = 50 \text{ M}\Omega$  e n = 12 bits.

## Esercizio 3

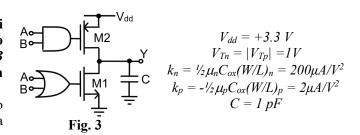

Si consideri il circuito logico mostrato in Fig. 3.

- a) Tracciare il grafico di Y(t) quotandone tutti i punti significativi e calcolare il tempo complessivo necessario perche' l'uscita raggiunga il valore di  $V_{dd}/2$  se  $A \in B$  commutano istantaneamente da 11 a 00, assumendo un ritardo di propagazione delle porte AND e OR di 8ns.

- b) Calcolare la potenza statica e dinamica dissipata nel caso in cui A e B siano cortocircuitati tra loro e pilotati da una onda quadra con f = 2 MHz e duty cycle 20%.