## Fondamenti di Elettronica - Ingegneria Elettronica - a.a. 2021/22 Secondo Appello - 9 settembre 2022

- 1. Riportare sulla prima pagina del foglio protocollo nome, cognome, numero di matricola, cod. persona. data, "Secondo Appello", numero totale di fogli consegnati.

- 2. Numerare tutti i fogli e riportare su ciascuno almeno nome, cognome, numero di matricola, cod. persona.

- 3. Scrivere con grafia leggibile e con la penna

- 4. Indicare chiaramente la domanda a cui si sta rispondendo. Ad esempio 1a)...

- 5. Risolvere per primi i punti in grassetto, perche' ritenuti piu' facili. La durata della prova e' 2.5 ore.

- 6. Non sono ammessi libri o appunti o altro materiale, eccetto la calcolatrice.

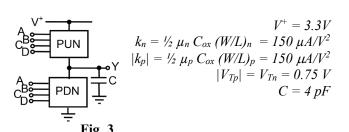

## Esercizio 1

Si consideri il circuito a MOSFET riportato nella Fig. 1, in cui  $v_{in}$  e' un generatore di tensione di piccolo segnale

- a) Determinare la polarizzazione del circuito (tensioni a tutti i nodi e correnti in tutti i rami), calcolando il valore che deve assumere il fattore di transconduttanza del pMOS per garantire  $V_{out} = 0$  V.

- b) Determinare l'espressione ed il valore del guadagno di piccolo segnale  $v_{out}/v_{in}$  a bassa frequenza, assumendo che il transistore pMOS sia caratterizzato da una resistenza di uscita,  $r_{\theta} = \infty$ .

- c) Tracciare il diagramma di Bode del modulo del trasferimento di piccolo segnale  $v_{out}/v_{in}$ , quotandone tutti i punti significativi, assumendo che il transistore pMOS sia caratterizzato da una resistenza di uscita,  $r_0 = \infty$ .

- d) Determinare la massima dinamica positiva e negativa del nodo di uscita.

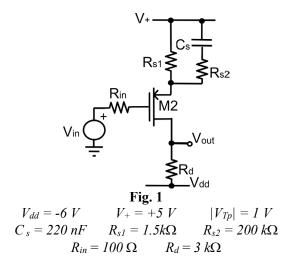

## Esercizio 2

Si consideri la catena di acquisizione mostrata nella Fig. 2. L'amplificatore operazionale saturi alle tensioni di alimentazione.  $V_{in}$  sia un generatore di segnale generico con ampiezza massima  $\delta \mu A$ . L'ADC sia del tipo ad approssimazioni successive con n=13 bits.

- a) Determinare l'espressione ed il valore del trasferimento ideale  $V_{out}/I_{in}$  a bassa frequenza ed il minimo valore del guadagno ad anello aperto  $A_{\theta}$  che l'amplificatore operazionale deve possedere perche' il guadagno reale sia pari ad almeno il 99.9% del guadagno ideale.

- b) Determinare il fattore di forma (W/L) necessario per il transistore del circuito di S&H, che garantisca una costante di tempo  $\tau$  di carica o scarica della capacita' di Hold pari a un colpo di clock, assumendo una tensione  $V_G$  in fase di Sample pari a SV.

- c) Determinare il minimo valore che deve assumere la capacita' di *Hold C<sub>H</sub>* per garantire una risoluzione del 2‰ in ingresso.

- d) Determinare il margine di fase dello stadio amplificatore se l'amplificatore operazionale e' caratterizzato da un prodotto guadagno-larghezza di banda,  $GBWP = 20 \ MHz \ (A_0 \ non \ e' noto \ separatamente)$ .

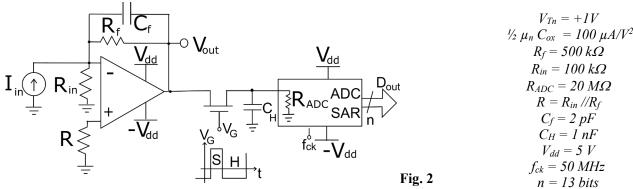

## Esercizio 3

Si consideri la porta logica in tecnologia CMOS mostrata in Fig. 3 che svolge la funzione logica  $Y = \overline{(A \cdot B + \overline{D})} + \overline{(A + C + B)}$ .

- a) Disegnare le reti di *pull-up* e di *pull-down* della porta logica complessa in tecnologia CMOS e in forma minima che svolga tale funzione logica. Si giustifichino le scelte effettuate.

- b) Determinare la massima frequenza di commutazione possibile dalla porta assumendo che tutti gli ingressi siano cortocircuitati tra loro e pilotati da un opportuno *clock*.